# Benchmarking Round 2 Candidates on Microcontrollers

**Çağdaş Çalık**\*, Munawar Hasan\*, Jinkeon Kang\*

NIST Lightweight Cryptography Workshop October 19, 2020

Guest Researcher, NIST

National Institute of Standards and Technology U.S. Department of Commerce

Updated on Nov 18, 2020

### Outline

- Motivation and Scope

- Implementations, Platforms, Test Cases

- The Benchmarking Framework

- Results

- Conclusion and Next Steps

Commercial equipment and software referred to in this paper are identified for informational purposes only and does not imply recommendation of or endorsement by the National Institute of Standards and Technology, nor does it imply that the products so identified are necessarily the best available for the purpose.

## Motivation and Scope

- Motivation

- Evaluate the performance of Round 2 candidates on microcontrollers

- Compare the candidates against existing NIST standards

- Goals

- High coverage of implementations

- Wide range of test cases

- Verification of the implementations and results

- Scope

- API compatible implementations

- Official versions of the algorithms

- This presentation: only primary variants

### Implementations

- Implementations were gathered from

- Submission packages

- Websites and GitHub repositories of the candidates

- Third party software benchmarking projects

| Language*     | AEAD<br>(89 Variants) | Hash<br>(19 Variants) | Total | AEAD-Primary<br>(32 Variants) | Hash-Primary<br>(12 Variants) |  |

|---------------|-----------------------|-----------------------|-------|-------------------------------|-------------------------------|--|

| С             | 161                   | 41                    | 202   | 66                            | 27                            |  |

| C / AVR       | 73                    | 15                    | 88    | 26                            | 10                            |  |

| C / ARM / AVR | 9                     | 4                     | 13    | 3                             | 2                             |  |

| ARM           | 35                    | 4                     | 39    | 18                            | 4                             |  |

| AVR           | 19                    | 16                    | 35    | 7                             | 7                             |  |

| Total         | 297                   | 80                    | 377   | 120                           | 50                            |  |

### **Implementations - Remarks**

- Primary variants of COMET<sup>\*</sup>, ESTATE, mixFeed, and SAEAES<sup>\*</sup> have only reference implementations.

- Problems faced in the benchmarking process

- Build errors

- Decryption failures

- Program crash

- Unsupported input sizes

- Test vector verification failures

### Platforms

| Board               | Microcontroller / Core                        | Frequency | Flash  | SRAM   |

|---------------------|-----------------------------------------------|-----------|--------|--------|

| Arduino Uno Rev3    | ATmega328P - AVR (8-bit)                      | 16 MHz    | 32 KB  | 2 KB   |

| Arduino Nano Every  | <u>ATMega4809</u> - AVR (8-bit)               | 20 MHz    | 48 KB  | 6 KB   |

| Arduino MKR Zero    | SAMD21 - ARM Cortex-M0+ (32-bit)              | 48 MHz    | 256 KB | 32 KB  |

| Arduino Due         | AT91SAM3X8E - ARM Cortex-M3 (32-bit)          | 84 MHz    | 512 KB | 96 KB  |

| Arduino Nano 33 BLE | <u>nRF52840</u> - ARM Cortex-M4F (32-bit)     | 64 MHz    | 1 MB   | 256 KB |

| HiFive1 Rev B       | <u>SiFive FE310-G002</u> - RV32 IMAC (32-bit) | 320 MHz   | 4 MB   | 16 KB  |

### Platforms

| Board               | Microcontroller / Core                        | Frequency | Flash  | SRAM   |

|---------------------|-----------------------------------------------|-----------|--------|--------|

| Arduino Uno Rev3    | ATmega328P - AVR (8-bit)                      | 16 MHz    | 32 KB  | 2 KB   |

| Arduino Nano Every  | <u>ATMega4809</u> - AVR (8-bit)               | 20 MHz    | 48 KB  | 6 KB   |

| Arduino MKR Zero    | SAMD21 - ARM Cortex-M0+ (32-bit)              | 48 MHz    | 256 KB | 32 KB  |

| Arduino Due         | AT91SAM3X8E - ARM Cortex-M3 (32-bit)          | 84 MHz    | 512 KB | 96 KB  |

| Arduino Nano 33 BLE | <u>nRF52840</u> - ARM Cortex-M4F (32-bit)     | 64 MHz    | 1 MB   | 256 KB |

| HiFive1 Rev B       | <u>SiFive FE310-G002</u> - RV32 IMAC (32-bit) | 320 MHz   | 4 MB   | 16 KB  |

- Time

- Varying input sizes for *Plaintext* and *Associated Data* for AEAD and Hash functions

- Short inputs: ranging from 0 to 128 bytes

- Long inputs\*: ranging from 256 to 2048 bytes with 128-byte increments

- Size

- For AEAD algorithms, the sizes for *enc-only*, *dec-only* implementations are calculated.

- Actual sizes are calculated by taking the difference w.r.t. the *empty cipher*.

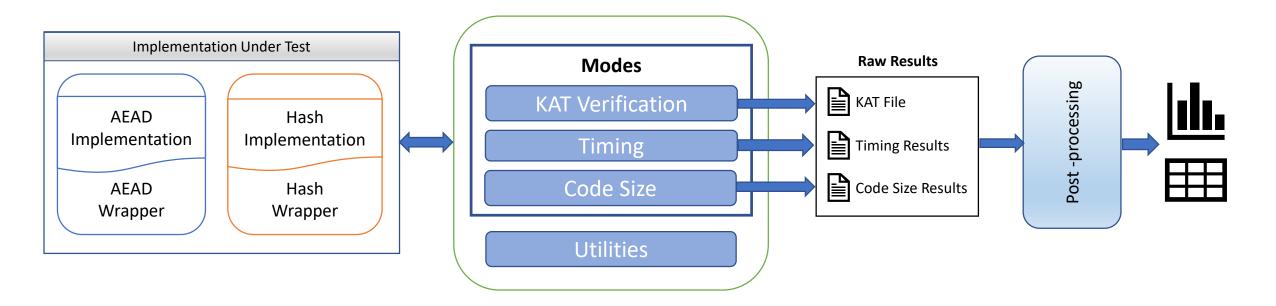

## The Benchmarking Framework

- The framework consists of C++ code for carrying out the experiments, and scripts for automating the build process and post-processing the results.

- It uses the PlatformIO embedded development platform and the GNU toolchains<sup>1,2,3</sup>.

<sup>1</sup> (GNU Tools for Arm Embedded Processors 7-2017-q4-major) 7.2.1 20170904 (release) [ARM/embedded-7-branch revision 255204]

<sup>2</sup> (GNU MCU Eclipse ARM Embedded GCC, 64-bit) 8.2.1 20181213 (release) [gcc-8-branch revision 267074]

<sup>3</sup> (AVR\_8\_bit\_GNU\_Toolchain\_3.6.2\_1759) 5.4.0

NIST

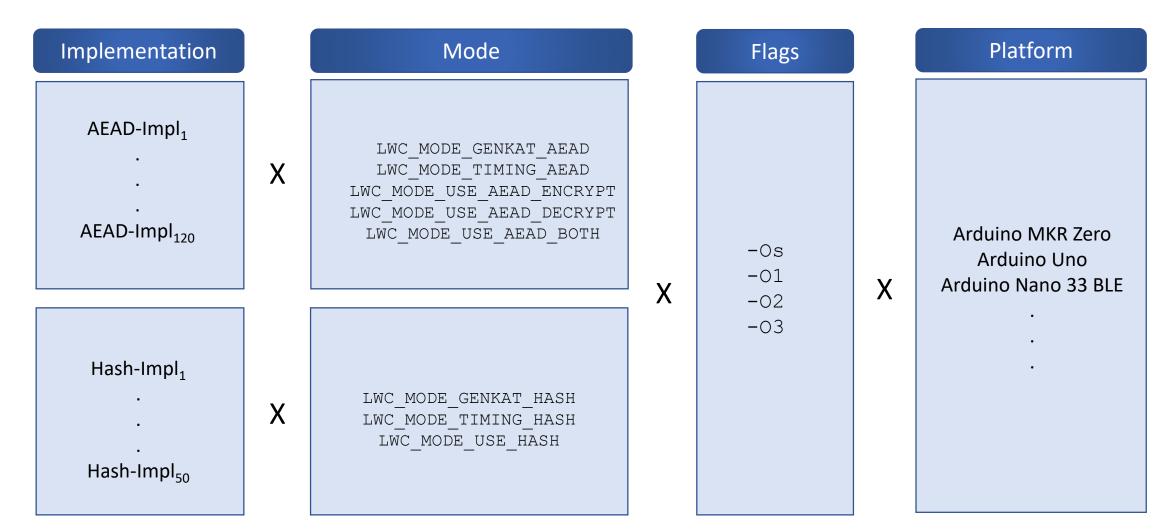

### **Build Configurations**

### **Benchmark Results**

- Code size (AEAD & Hash)

- Timing (AEAD & Hash)

- Pairwise-comparison of AEAD algorithms against AES-GCM (AEAD only)

- Benchmarks include AES-GCM and SHA-256 from Mbed-TLS library for comparison.

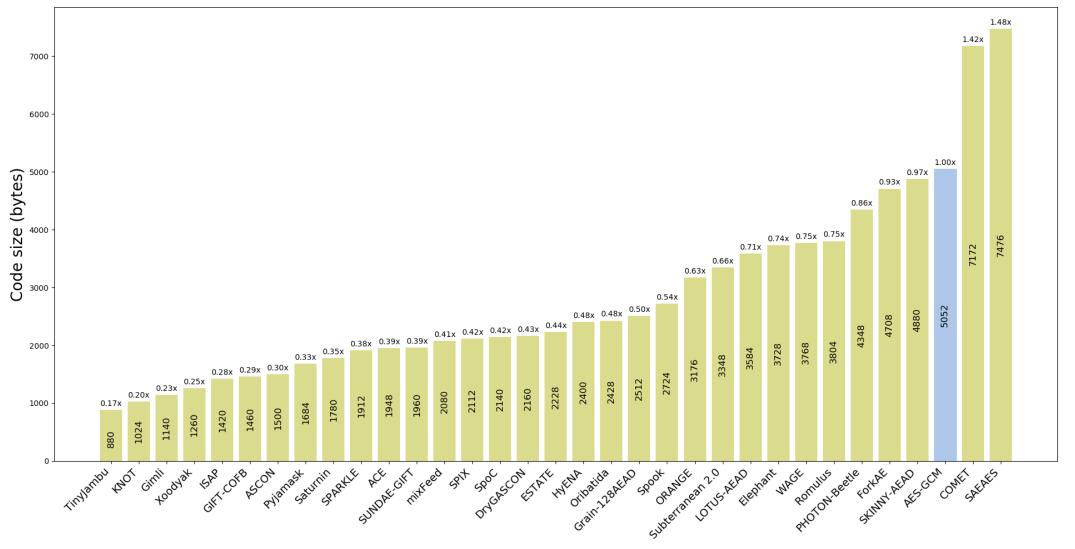

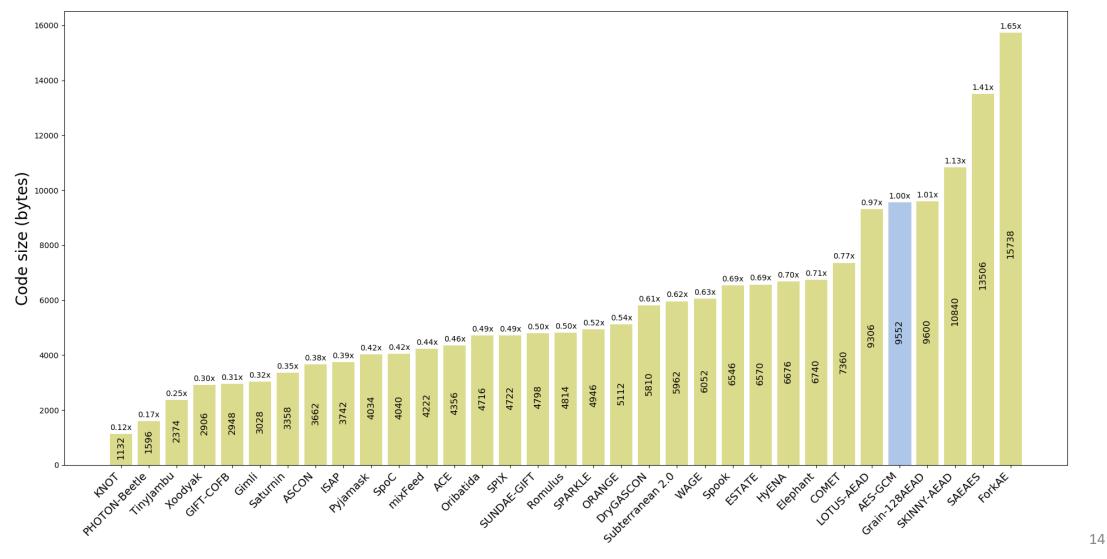

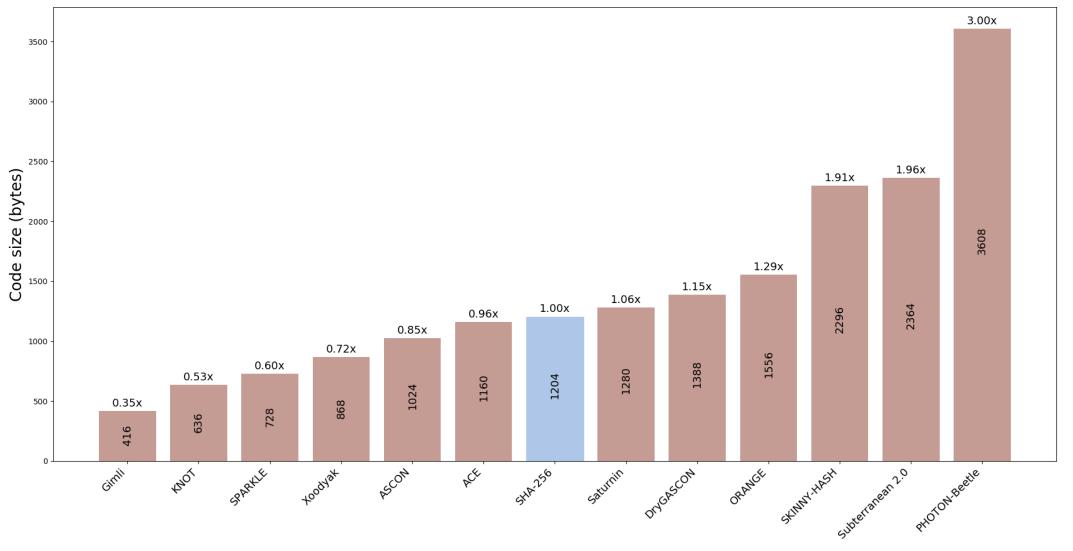

### Code Size for Primary AEAD Variants<sup>\*</sup> on Cortex-M0+

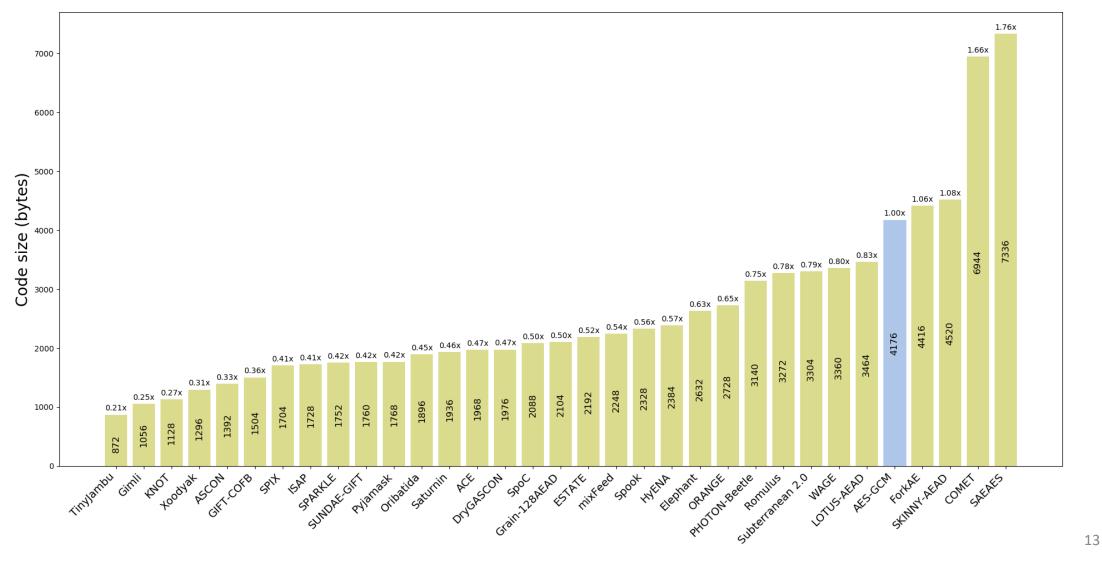

### Code Size for Primary AEAD Variants<sup>\*</sup> on Cortex-M4F

#### Code Size for Primary AEAD Variants<sup>\*</sup> on AVR

\* Smallest sized implementation of each variant among all its implementations compiled with four different optimization flags

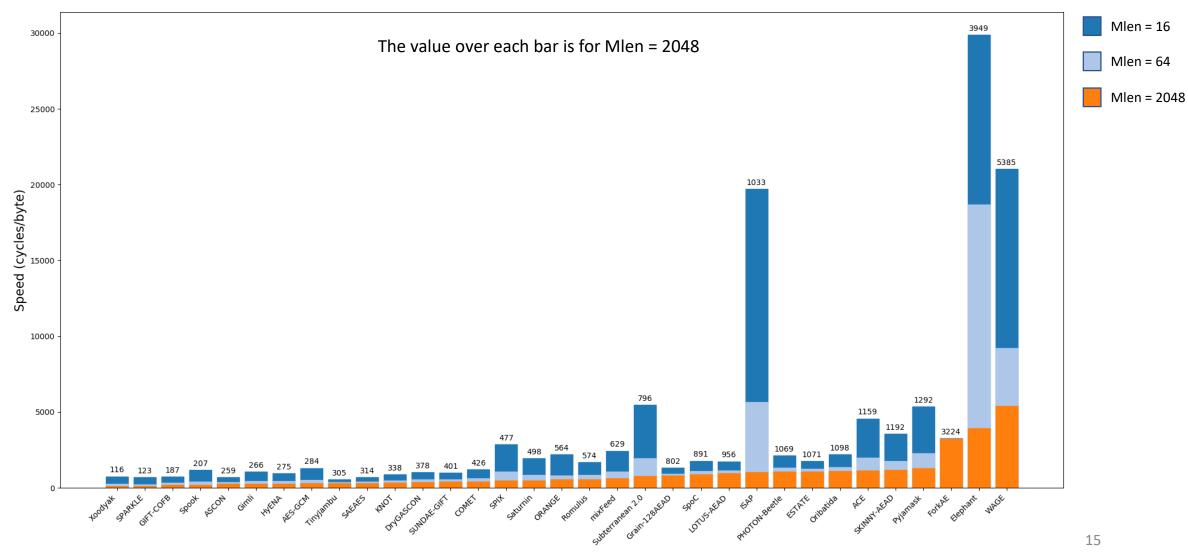

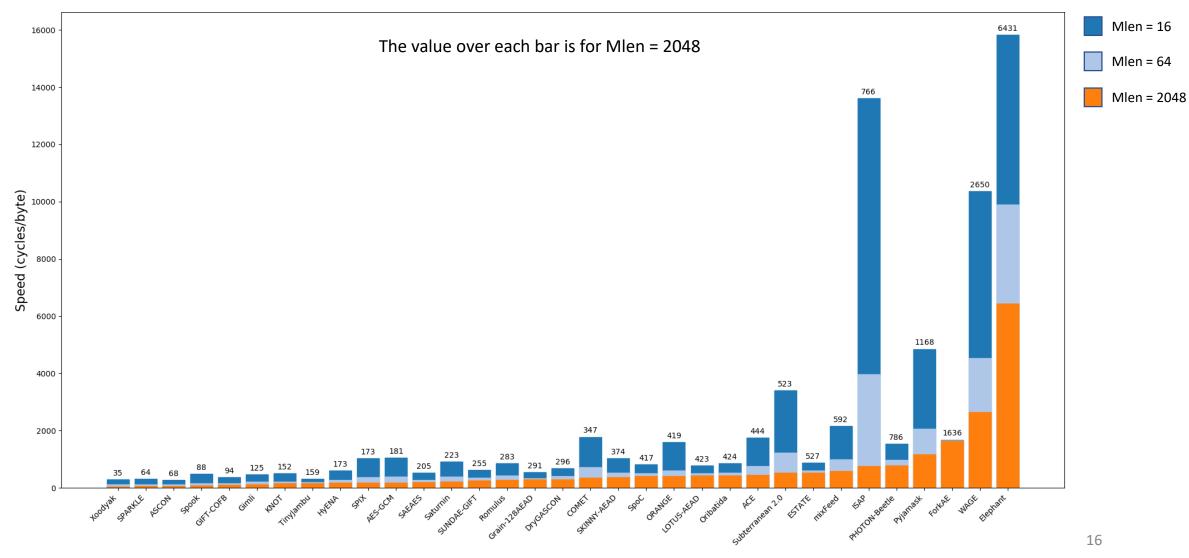

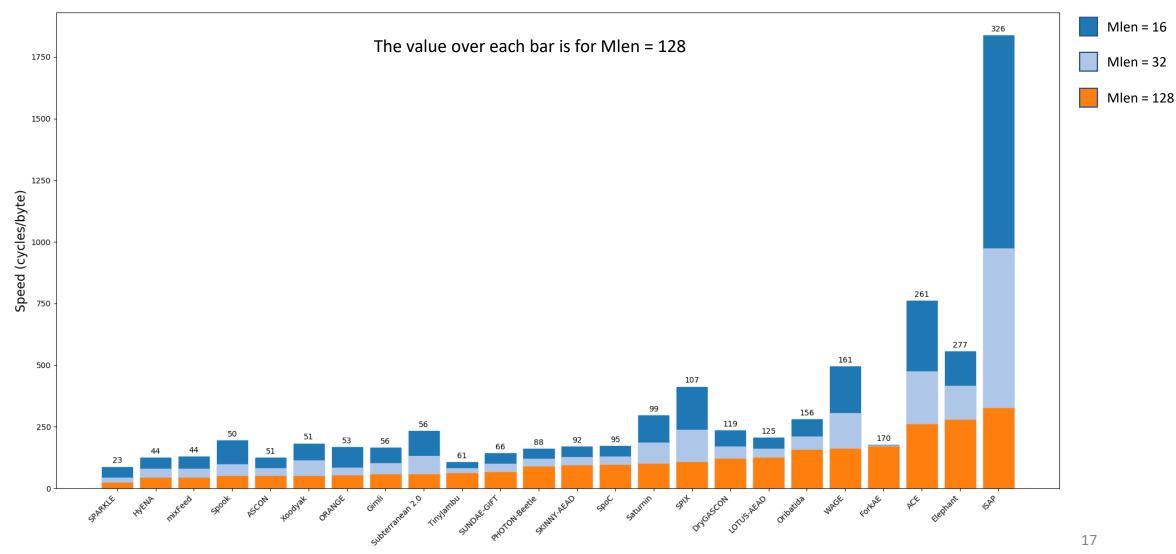

#### Timings for Primary AEAD Variants<sup>\*</sup> on Cortex-M0+ (AD Length=0, Msg Length=16, 64, 2048)

#### Timings for Primary AEAD Variants<sup>\*</sup> on Cortex-M4F (AD Length=0, Msg Length=16, 64, 2048)

#### Timings for Primary AEAD Variants<sup>\*</sup> on AVR (AD Length=0, Msg Length=16, 32, 128)

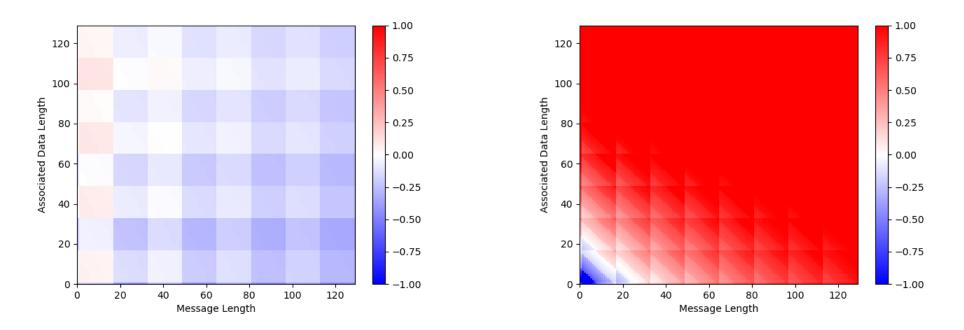

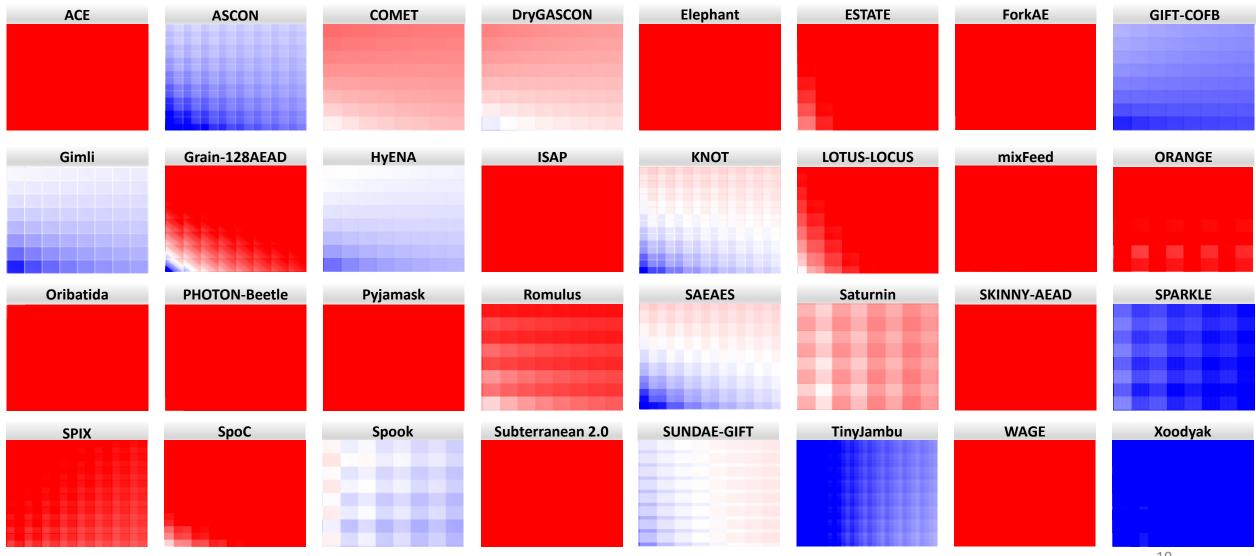

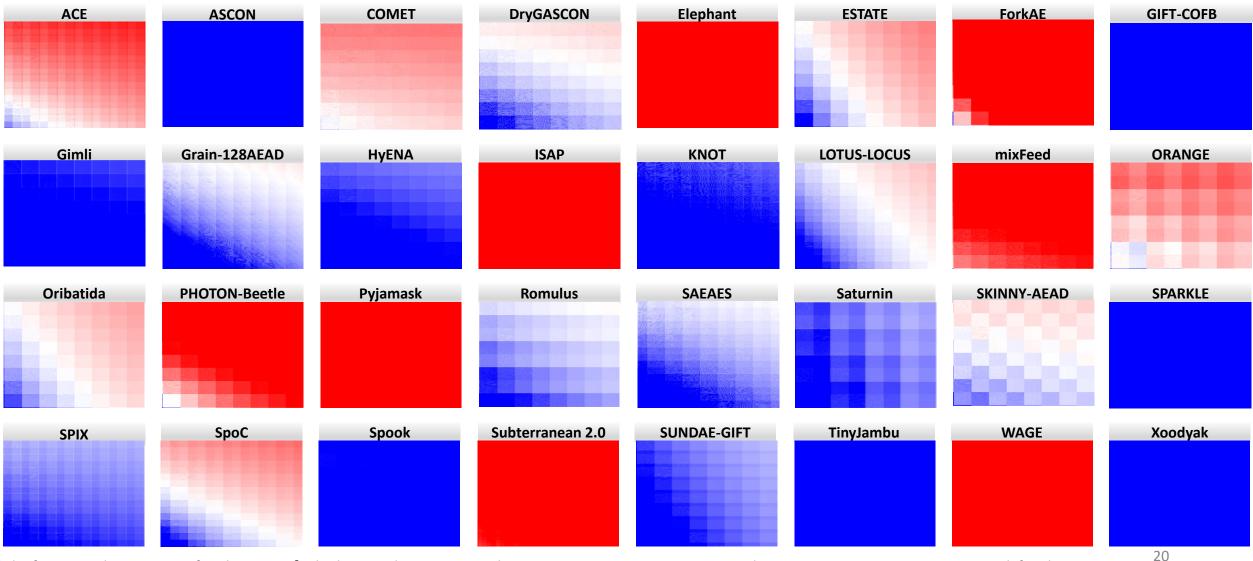

### Pairwise Comparison of AEAD Algorithms NIST

• A 2D plot is created by comparing the execution times of two AEAD algorithms for each *Plaintext* and *Associated Data* length from 0 to 128 bytes.

#### Primary AEAD Variants<sup>1</sup> v. AES-GCM<sup>2</sup> on Cortex-MO+

<sup>1</sup>The fastest implementation of each variant. <sup>2</sup> Mbed TLS implementation with MBEDTLS AES ROM TABLES and MBEDTLS AES FEWER TABLES defined.

#### Primary AEAD Variants<sup>1</sup> v. AES-GCM<sup>2</sup> on Cortex-M4F NIST

<sup>1</sup>The fastest implementation of each variant. <sup>2</sup>Mbed TLS implementation with MBEDTLS AES ROM TABLES and MBEDTLS AES FEWER TABLES defined.

#### Code Size for Primary Hash Variants<sup>\*</sup> on Cortex-M0+

\* Smallest sized implementation of each variant among all its implementations compiled with four different optimization flags.

21

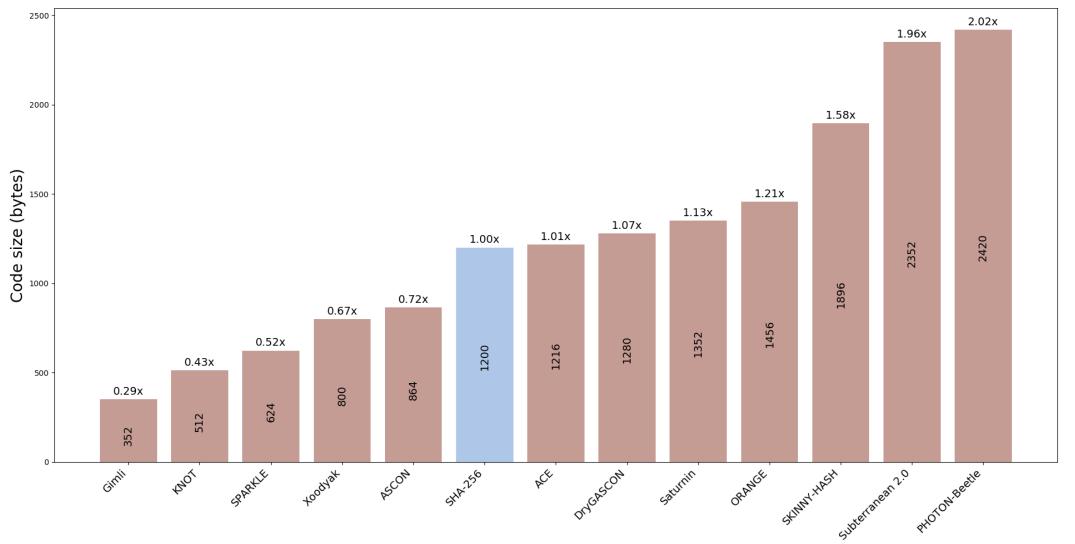

### Code Size for Primary Hash Variants<sup>\*</sup> on Cortex-M4F

\* Smallest sized implementation of each variant among all its implementations compiled with four different optimization flags.

22

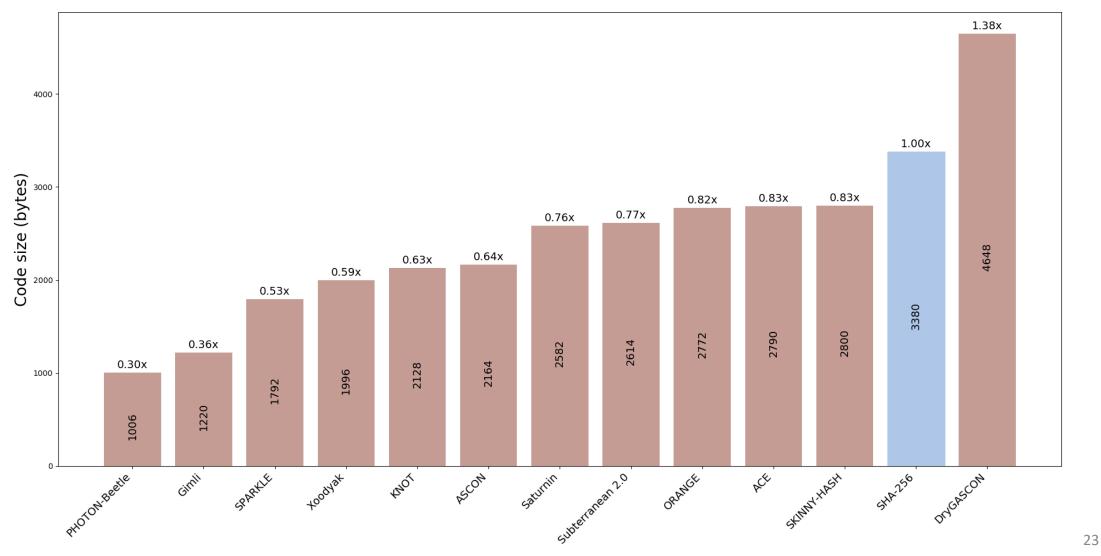

#### Code Size for Primary Hash Variants<sup>\*</sup> Variants on AVR **NIST**

### Timings for Primary Hash Variants<sup>\*</sup> on Cortex-M0+ (Msg Length=16, 64, 2048)

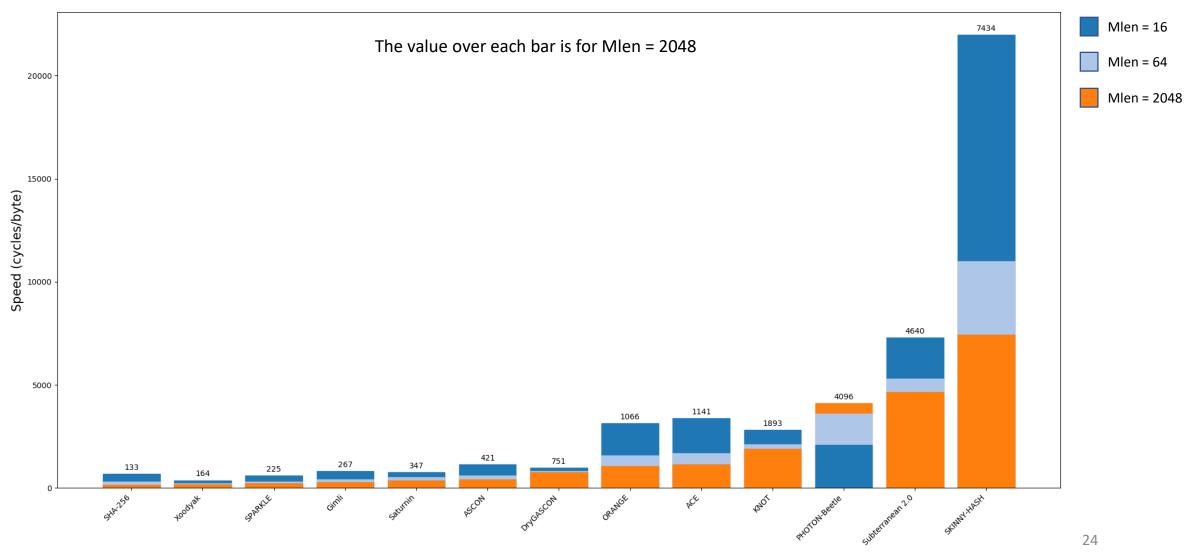

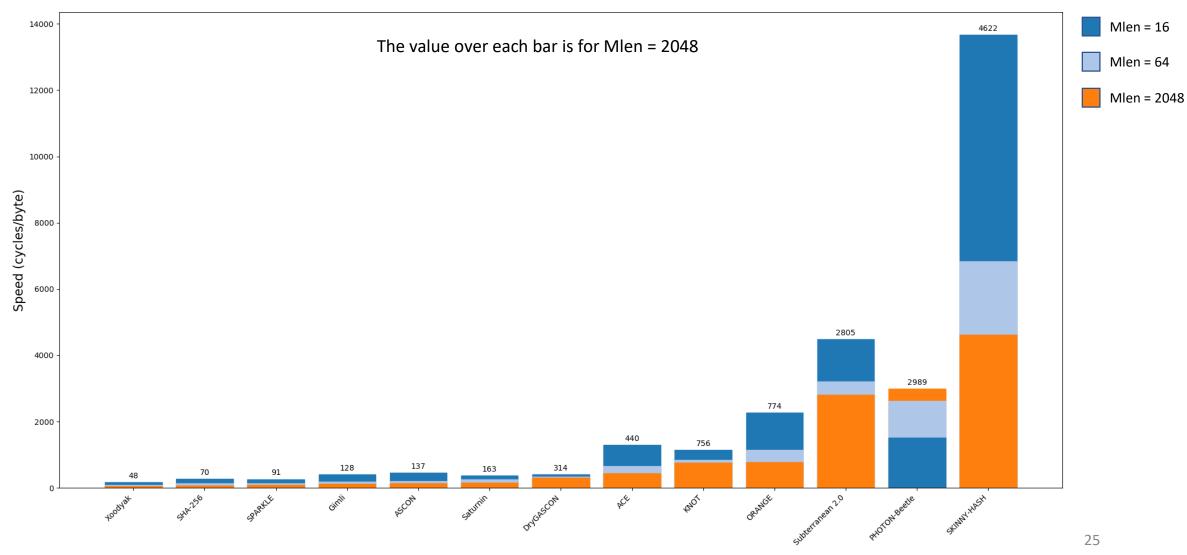

# Timings for Primary Hash Variants<sup>\*</sup> on Cortex-M4F (Msg Length=16, 64, 2048)

# Summary of Results

Benchmarking is challenging, due to the range of platforms, implementation tradeoffs, and different use cases.

#### AEAD

- Most of the candidates achieved smaller *code size* compared to AES-GCM<sup>\*</sup>.

- On ARM Cortex-M0+ about half of the candidates and on ARM Cortex-M4F most candidates showed performance improvement at least in some of the test cases over AES-GCM<sup>\*</sup>.

#### Hash

- Depending on the platform, four to seven candidates had smaller code size than SHA-256<sup>\*</sup>.

- Most of the candidates performed worse compared to SHA-256 in timing experiments.

## **Conclusion and Next Steps**

- Fair and extensive performance evaluation of the candidates on microcontrollers will contribute to the selection of the finalists.

- The benchmark results published by the submitters, third party benchmarking projects, and academic papers are also taken into consideration in the evaluation process.

- The benchmarking framework and the results will be available at: <u>https://github.com/usnistgov/Lightweight-Cryptography-Benchmarking</u>

- Next Steps

- Keep the implementation database up to date

- Resolve the issues for implementations where benchmarking could not be performed

- Add new platforms

- Verify and publish the results

**Project webpage:** <u>https://csrc.nist.gov/projects/lightweight-cryptography</u>

**GitHub:** <u>https://github.com/usnistgov/Lightweight-Cryptography-Benchmarking</u>

Forum: <a href="https://www.inst.gov">www.inst.gov</a>

**Contact email:** <u>lightweight-crypto@nist.gov</u>