PROCEEDINGS

# **OF THE**

# FOURTH SEMINAR ON THE DOD COMPUTER SECURITY INITIATIVE

NATIONAL BUREAU OF STANDARDS GAITHERSBURG, MARYLAND

AUGUST 10 - 12, 1981

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

#### TABLE OF CONTENTS

|                                                                                                                                                 | Page        |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Table of Contents                                                                                                                               | i           |

| About the DoD Computer Security Initiative                                                                                                      | iii         |

| About the Seminar                                                                                                                               | iii         |

| Acknowledgments                                                                                                                                 | iv          |

| Program                                                                                                                                         | v           |

| List of Handouts                                                                                                                                | viii        |

| "Welcoming Address," James H. Burrows, Director, Institute<br>for Computer Sciences and Technology, National Bureau of<br>Standards             | A-1         |

| "Keynote Address," Admiral Bobby Inman, Deputy Director of<br>Central Intelligence, Washington, D.C.                                            | B-1         |

| "Introductory Comments," Stephen T. Walker, Director,<br>Information Systems, Office of Deputy Under Secretary of<br>Defense (C <sup>3</sup> I) | C-1         |

| "Burroughs' Efforts in Computer Security," Chris Tomlinson                                                                                      | D-1         |

| "CR80-A Fault Tolerant Computer for Implementation in Secure<br>Systems," Asbjørn Smitt, Christian-Rovsing A/S, Ballerup,<br>Denmark            | E-1         |

| "Computer Security and Control Data," Terry A. Cureton,<br>Control Data Corporation                                                             | F <b>-1</b> |

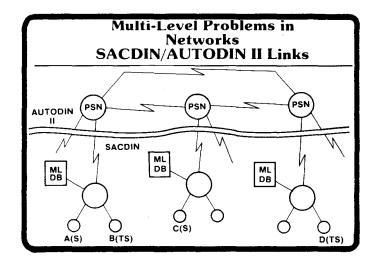

| "SAC Digital Network Security Methodology," Mauro Ferdman,<br>The MITRE Corporation                                                             | G-1         |

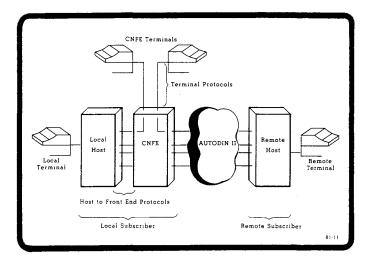

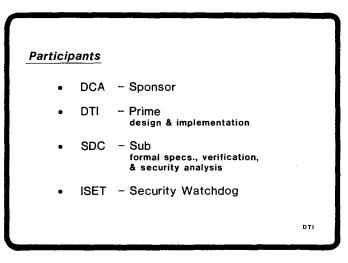

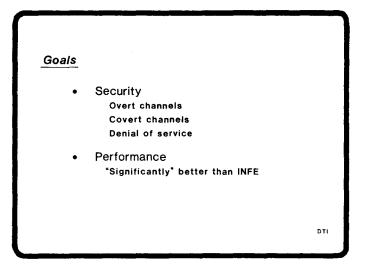

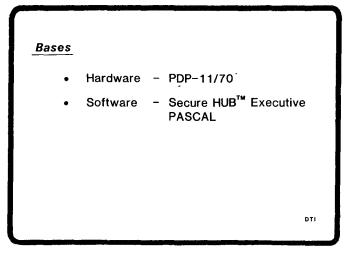

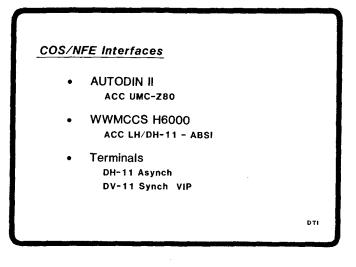

| "COS/NFE Overview," Gary Grossman, Digital Technology,<br>Incorporated                                                                          | H-1         |

| "WIS Security Strategy," Larry Bernosky, Defense Communications<br>Agency                                                                       | I-1         |

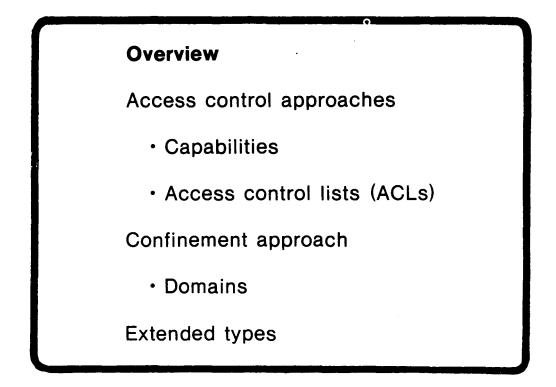

| "Trusted Computing Research at Data General Corporation,"<br>Leslie DeLashmutt and Doug Wells, Data General Corporation                         | J-1         |

| "The iAPX-432 Microcomputer System," George Cox, Intel<br>Corporation                                                                           | K-1         |

| "ICL Efforts in Computer Security," Tom Parker, International<br>Computers, Limited                                                            | L-1 |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| "GNOSIS: A Progress Report," Bob Colten, TYMSHARE                                                                                              | M-1 |

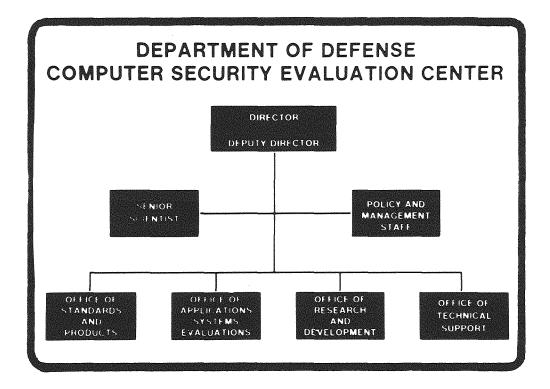

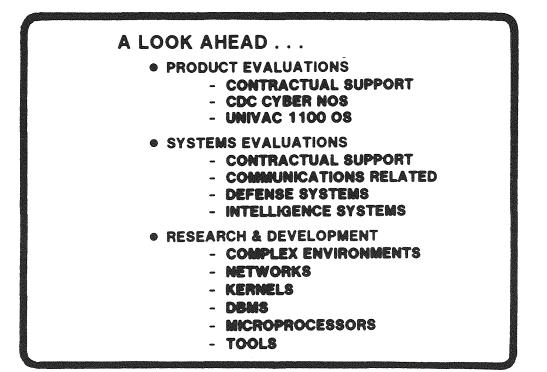

| "Computer Security Evaluation Center," George Cotter,<br>Acting Director, DoD Computer Security Evaluation Center,<br>National Security Agency | N-1 |

| "Trusted Computer Systems," Rein Turn, The RAND Corporation                                                                                    | 0-1 |

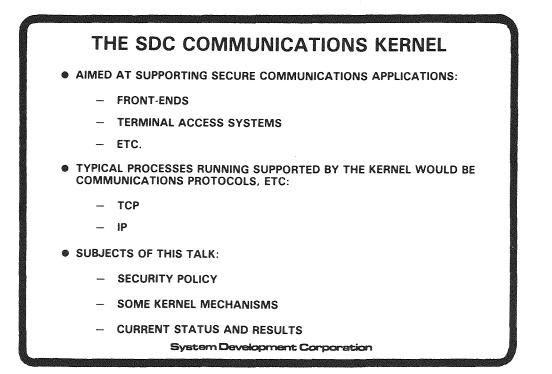

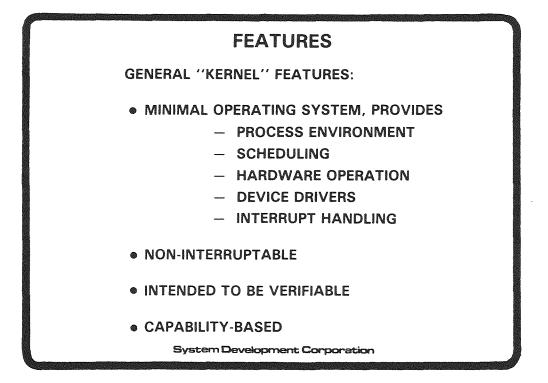

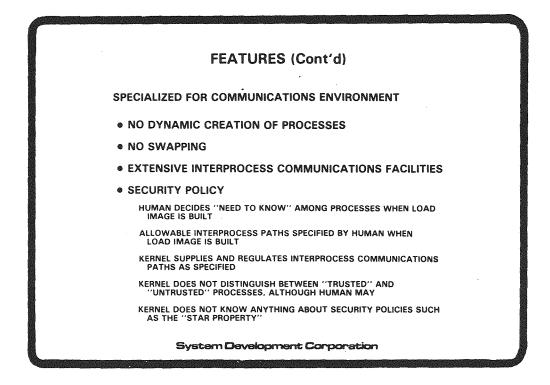

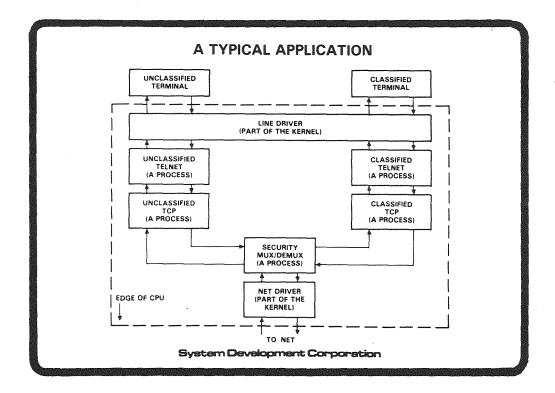

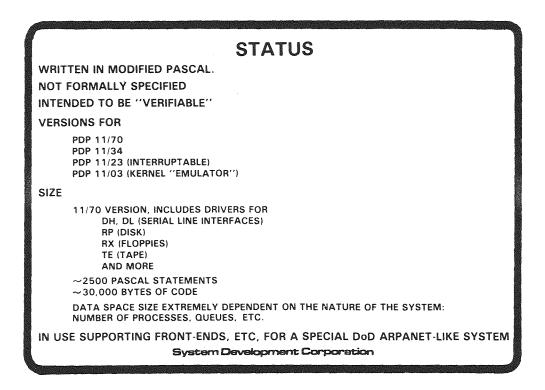

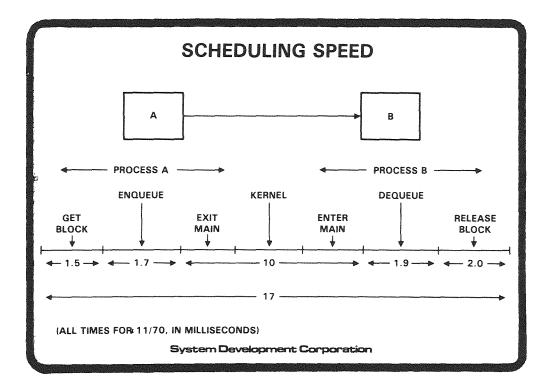

| "The SDC Communications Kernel," David L. Golber, System<br>Development Corporation                                                            | P-1 |

| "The MITRE Trusted Packet Switch," Chris Hisgen, The MITRE<br>Corporation                                                                      | Q-1 |

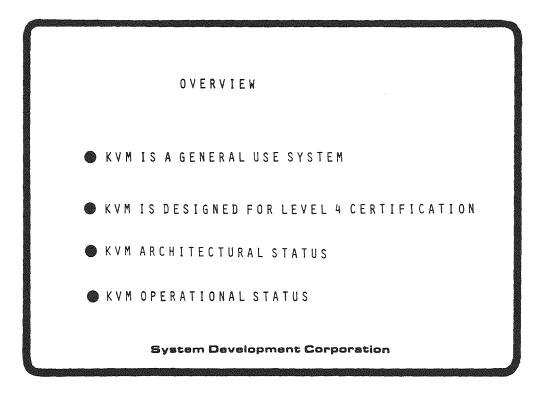

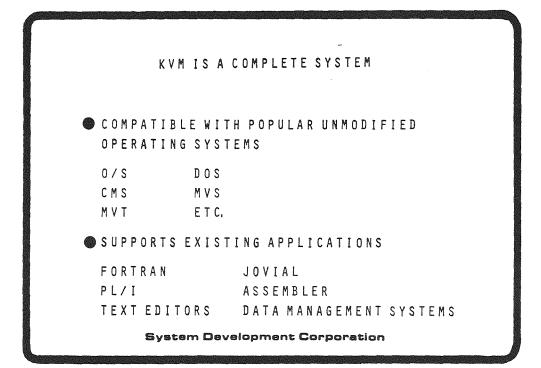

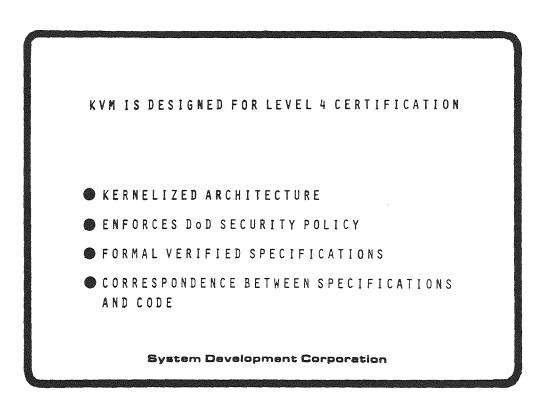

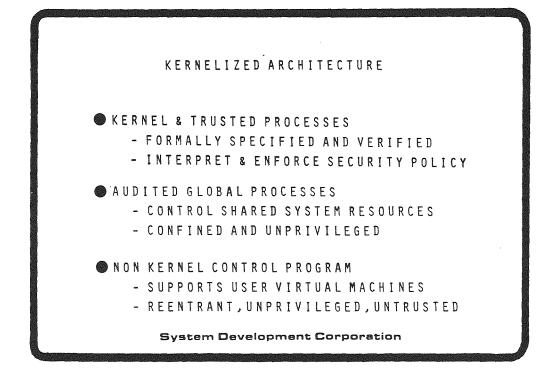

| "Experience with KVM," Tom Hinke, System Development Corporation                                                                               | R-1 |

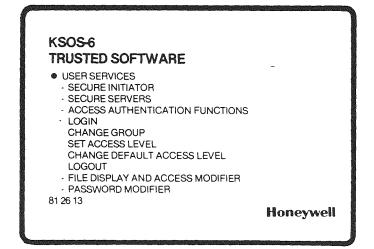

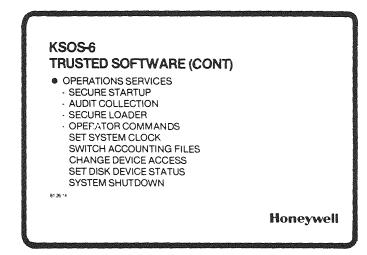

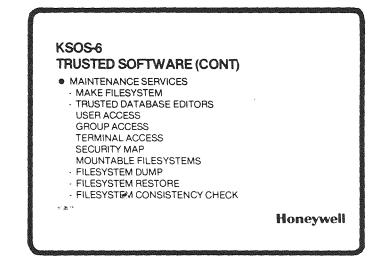

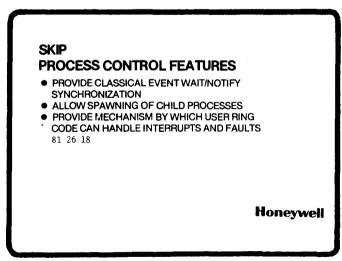

| "SCOMP (KSOS-6) Development Experience Update," Lester Friam,<br>Honeywell                                                                     | S-1 |

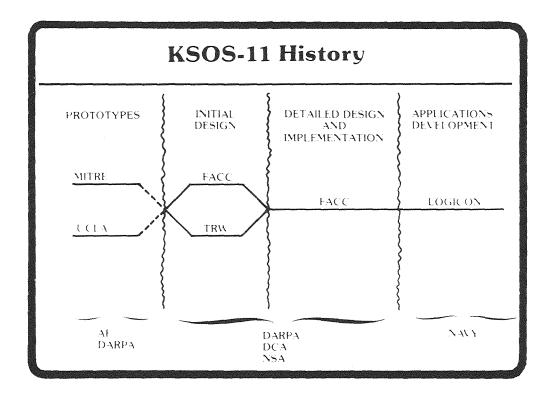

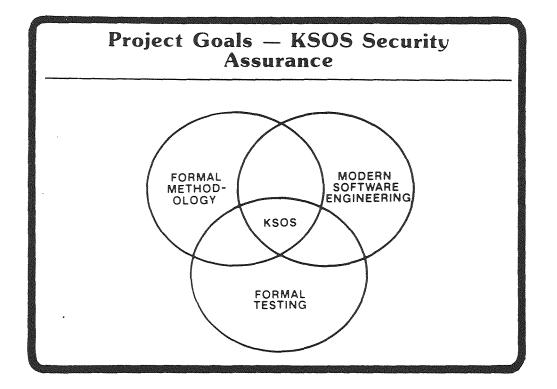

| "KSOS-11 Summary and Update," John Woodward, The MITRE<br>Corporation                                                                          | T-1 |

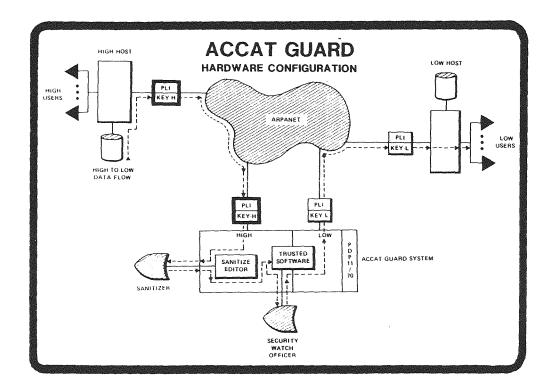

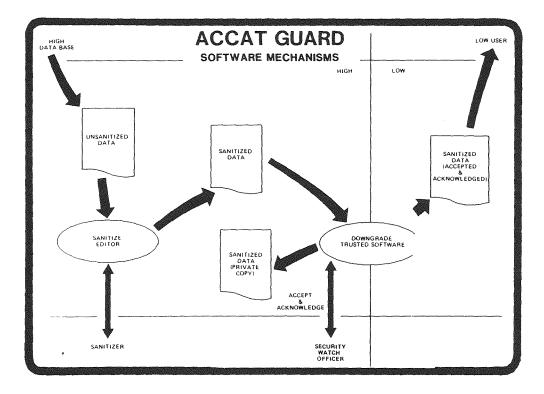

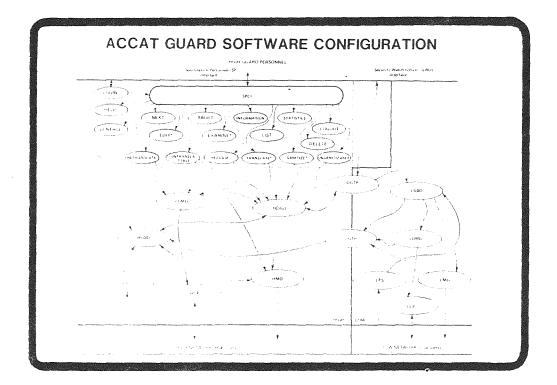

| "ACCAT and FORSCOM Guard Systems," Mike Soleglad, Logicon                                                                                      | U-1 |

| "A Security Model for a Military Message System,"<br>Carl E. Landwehr, Naval Research Laboratory                                               | V-1 |

| "EUCLID and Verification", Ian Griggs, I.P. Sharp &<br>Associates, Ltd.                                                                        | W-1 |

| "The Evaluation of Three Specification and Verification<br>Methodologies," Richard A. Platek, Digicomp Research Corporation                    | X-1 |

ii

#### DOD COMPUTER SECURITY INITIATIVE SEMINAR - IV

#### August 10-12, 1981

#### ABOUT THE DOD COMPUTER SECURITY INITIATIVE

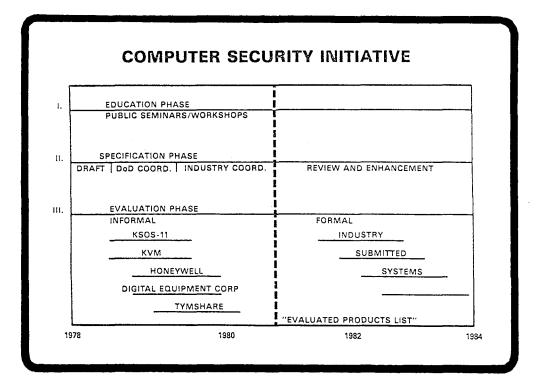

The Department of Defense (DoD) Computer Security Initiative was established in 1978 by the Assistant Security of Defense for Communications, Command, and Control and Intelligence to achieve the widespread availability of "trusted" ADP systems for use within the DoD. Widespread availability implies the use of commercially developed trusted ADP systems whenever possible. Recent DoD research activities are demonstrating that trusted ADP systems can be developed and successfully employed in sensitive information handling environments. In addition to these demonstration systems, a technically sound and consistent evaluation procedure must be established for determining the environments for which a particular trusted system is suitable.

The Computer Security Initiative is attempting to foster the development of trusted ADP systems through technology transfer efforts and to define reasonable ADP system evaluation procedures to be applied to both government and commercially developed trusted ADP systems. This seminar is the fourth in a series which constitute an essential element in the Initiative's Technology Transfer Program.

Effective January 1, 1981, the Director of the National Security Agency was assigned responsibility for computer security evaluation for the Department of Defense. Plans for the transfer of the Computer Security Initiative activities to NSA are well underway.

The Institute for Computer Sciences and Technology, through its Computer Security and Risk Management Standards program, seeks new technology to satisfy Federal ADP security requirements. The Institute then promulgates acceptable and cost effective technology in Federal Information Processing Standards and Guidelines. The Institute is pleased to assist the Department of Defense in transferring the interim results of its research being conducted under the Computer Security Initiative.

#### ABOUT THE SEMINAR

This is the fourth in a series of seminars to acquaint computer system developers and users with the status of trusted ADP system developments plans for the integrity evaluation of trusted systems. The three previous seminars have stressed user requirements for trusted systems throughout the government and the private sector, experience with design of production prototype trusted systems, and industry progress in computer security. The focus of this seminar is on trusted system efforts across the board.

#### ACKNOWLEDGMENTS

A number of people in and outside of the DoD Computer Security Technical Consortium have helped to make this seminar a success. At the MITRE Corporation, Pete Tasker helped to organize the speakers; Karen Borgeson and Dianne Mazzone managed registration; Charles McClure provided behind-the-scenes support. Finally Dr. Billy Claybrook handled the entire job of collecting and organizing the material for this Proceedings.

Also, we are grateful to Greta Pignone and Sara R. Torrence of NBS for arranging the splendid facilities.

#### DISCLAIMER

The presentations in this proceedings are provided for your information. They should not be interpreted as necessarily representing the official view or carrying any endorsement, either expressed or implied, of the Department of Defense or the United States Government.

T. Walk

Stephen T. Walker Chairman DoD Computer Security Technical

Consortium

#### DOD COMPUTER SECURITY INITIATIVE SEMINAR - IV

August 10-12, 1981

Monday, August 10

9:30 INTRODUCTION

> Jim Burrows, Director Institute for Computer Sciences and Technology National Bureau of Standards

KEYNOTE SPEAKER

Admiral Bobby Inman Deputy Director of Central Intelligence

DOD Computer Security Initiative Status

Steve Walker, Chairman

DoD Computer Security Technical Consortium

MANUFACTURERS' EFFORTS IN COMPUTER SECURITY

Chris Tomlinson Burroughs Corporation

Axel Hvidtfeldt Christian-Rovsing

Terry Cureton Control Data Corporation

2:00

#### ACQUISITION & DEVELOPMENT EXPERIENCE

SACDIN

Mauro Ferdman The MITRE Corporation

Communications Operating System/NFE

Gary Grossman Digital Technology Incorporated

WWMCCS INFORMATION SYSTEM COMPUTER SECURITY

Larry Bernosky WWMCCS System Engineering Office

#### Tuesday, August 11

9:15 NBS COMPUTER SECURITY EFFORTS

Dennis Branstad National Bureau of Standards

MANUFACTURERS' EFFORTS IN COMPUTER SECURITY (Continued)

Les DeLashmutt Data General Corporation

George Cox Intel Corporation

Tom Parker International Computers Limited

Bob Colten & Norm Hardy Tymshare

#### 2:00 DOD COMPUTER SECURITY EVALUATION CENTER

George Cotter, Acting Director DOD Computer Security Evaluation Center National Security Agency

NON-DOD TRUSTED SYSTEM NEEDS

Rein Turn The Rand Corporation (Consultant)

COMMUNICATIONS EXPERIENCE

The SDC Communications Kernel

David L. Golber System Development Corporation

The MITRE Trusted Packet Switch

Chris Hisgen The MITRE Corporation

5:30 Wine & Cheese Reception Washingtonian Hotel (until 7:30 p.m.)

#### Wednesday, August 12

#### 9:15

2:00

#### DEVELOPMENT EXPERIENCE UPDATE

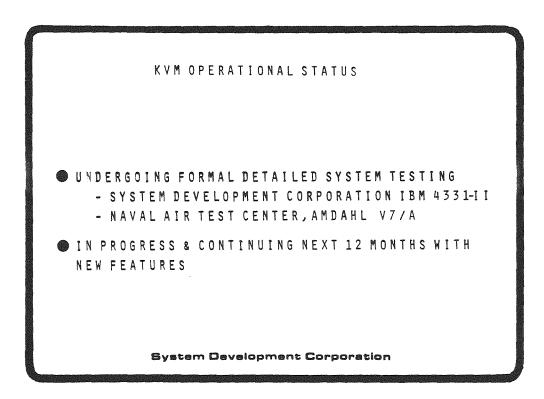

KVM/370

Tom Hinke System Development Corporation

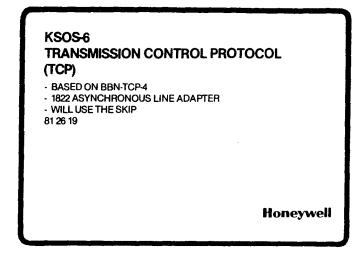

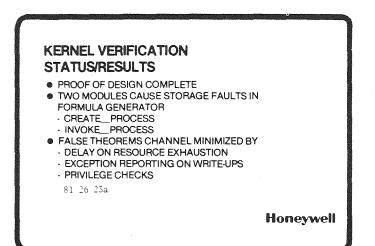

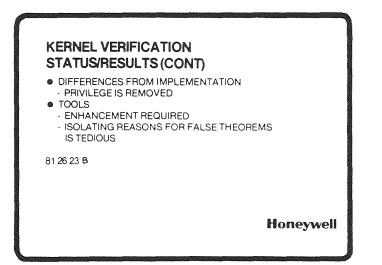

KSOS-6

Les Fraim Honeywell Information Systems

KSOS-11

John Woodward The MITRE Corporation

RESEARCH AND DEVELOPMENT UPDATE

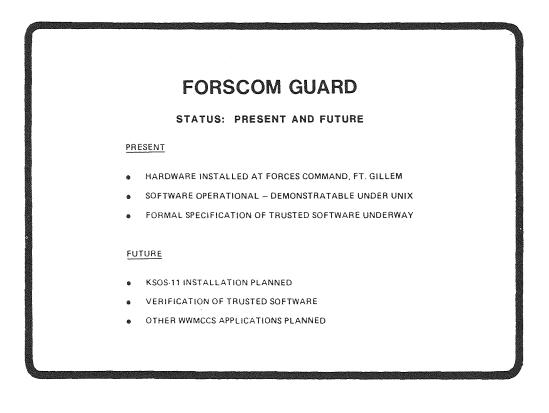

ACCAT Guard & FORSCOM Security Monitor

Mike Soleglad Logicon

Security Model for a Military Message System

Carl Landwehr Naval Research Lab

RESEARCH AND DEVELOPMENT UPDATE (continued)

Euclid & Verification

Ian Griggs I. P. Sharp & Associates, Ltd

Evaluation of Specification & Verification Systems

Richard Platek Digicomp Research

WRAP-UP

#### LIST OF HANDOUTS

REIN TURN

TRUSTED COMPUTER SYSTEMS: NEEDS AND INCENTIVES FOR USE IN GOVERNMENT AND THE PRIVATE SECTOR, JUNE 1981

#### Welcoming Address Fourth Seminar on the DoD Computer Security Initiative August 10, 1981

James H. Burrows Director, Institute for Computer Sciences and Technology

I am pleased to welcome you to the Fourth Seminar on the Department of Defense Computer Security Initiative Program. As in the past, the National Bureau of Standards and the Institute for Computer Sciences and Technology are happy to collaborate with Office of the Secretary of Defense in bringing information about trusted computer systems to users and system developers. I am told that there is a plan to hold a fifth seminar in this series next Spring to continue these valuable information exchanges.

The program announcing this seminar also announced the establishment of the computer security evaluation center for the defense and intelligence communities at the National Security Agency, a subject to be addressed by our distinguished keynote speaker this morning. We are glad that this has come to fruition, and hope that we will be able to continue to work with the evaluation center through the security initiative in diffusing trusted system technology to the user community.

Computer security is no longer an exclusive concern of the defense and intelligence communities. These agencies, of course, have rigorous requirements for protecting the secrecy of data. However, as we become more dependent upon computers for handling financial, health, and other critical information, techniques for assuring the integrity and reliability of computer systems become essential throughout the government and private sector.

A-1

Not only do the defense agencies in the Federal Government need off-the-shelf solutions to their security problems, but so do the ADP users in the civil government agencies and the private sector. NBS can play a role in getting information about this needed technology to users through technical interchanges such as this seminar, through the publication of technical reports, and through the development of computer security standards and guidelines when the technology is appropriately developed.

The Paperwork Reduction Act of 1980 (P.L. 96-511) passed last year reflects Congress' concerns that computer security efforts be integrated into the overall information resources management concept. Among the responsibilities, centered on the Office of Management and Budget, in implementing the Act are the functions of developing and implementing policies, principles, standards, and guidelines on information disclosure and confidentiality, and on safeguarding the security of information collected and maintained by the agencies. With its emphasis on planning for information technology acquisition and use, the Act provides the impetus for including essential activities such as planning for computer security into agency long-range planning for information management activities.

I believe that computer security is a pervasive problem that needs top level attention from managers, as well as from technical staff. It is a problem that encompasses the entire information processing cycle from intake of data through the processing of data, the delivery of the information product, and the storage of data. While the need is pervasive, it is also clear that achieving a secure system is costly in both time and money.

A-2

Since the technology of computer security is not available in existing computer systems, we have tried to attack the problem of computer security through a variety of administrative and management controls which will continue to be essential elements for achieving secure systems. Trusted system technology, however, offers promising capabilities for maintaining the integrity and reliability of critical systems. That assuring integrity and reliability is important is evident in the estimates that problems associated with errors, ommissions, and modifications of data occur ten times more frequently than intentional disclosures.

I, therefore, stongly support this R&D and technology transfer effort and hope that this is a successful and fruitful seminar.

NG.

I now have the honor of introducing our distinguished keynote speaker, Admiral Bobby R. Inman, who has broad experience both in the defense and intelligence communities. Admiral Inman, a graduate of the University of Texas, Austin, began his career in the U.S. Navy in 1952. Since then, he has held the positions of Director of Naval Intelligence, Vice Director of the Defense Intelligence Agency for Plans, Operations and Support, and the Director of the National Security Agency. He is currently the Deputy Director of Central Intelligence. Let's welcome Admiral Inman to this seminar.

A-3

#### **KEYNOTE ADDRESS**

#### COMPUTER SECURITY INITIATIVE

Admiral Bobby Inman Deputy Director of Central Intelligence Washington, D.C.

It is a pleasure to welcome you to this Seminar and to speak briefly with you about computer security, the recent developments within the Department of Defense and the Intelligence Community and the challenges that lie ahead.

As Dr. Gerald P. Dinneen, former Assistant Secretary of Defense for C<sup>3</sup>I defined at the first of these Seminars two years ago, a "trusted" computer system is one with sufficient hardware and software integrity to allow its use for the simultaneous processing of multiple levels of classified or sensitive information.

The need for trusted computer systems is very real and growing rapidly. Factors influencing this need are:

- the growing use of automated information handling systems throughout the DoD and the Intelligence Community and in particular the linking of these systems into major networks;

- increasing requirements for controlling access to compartmented and sensitive information;

- the requirement for broader dissemination of information both within and beyond the community;

- growing difficulties with obtaining required numbers of cleared personnel, both military and civilian.

Despite continuing internal efforts to develop special purpose trusted systems for unique needs, we already rely very heavily on the products of the computer industry to meet our information processing requirements, and this

dependence will continue to grow significantly in the future. It is therefore very gratifying to observe the progress being made by the computer industry in applying computer security technology as represented by the industry presentations at this and the previous Seminars.

It is very important, also, that the Department of Defense and the Intelligence Community develop sufficient expertise to be able to evaluate the integrity of computer software and systems developed by industry and government, and that we be able to determine suitable physical and administrative environments for their application. We have had scattered efforts over the past several years to evaluate specific systems for specific installations. But these efforts have always been more or less ad hoc, and because of the extensive technical background required, expensive to carry out.

I am very pleased therefore to announce today the establishment of a Computer Security Technical Evaluation Center for the Department of Defense and the Intelligence Community at the National Security Agency. Last fall, as Director of NSA, I enthusiastically endorsed the establishment of this Center at NSA as a new and separate function. I am very pleased with the progress being made in setting up the Center and I remain strongly committed to its success.

I would like to make several observations about the Center and some of its relationships:

Because the private sector computer manufacturing community is the primary source of ADP systems, the Center's role will be to work with the manufacturers, deriving as much system integrity as possible from industry developed systems. This is a rather sharp contrast to the NSA's more traditional communications security role where the government has the dominant technical role.

- The Center will have a difficult task developing procedures which assure protection of sensitive portions of a system which the government does not own. Simply classifying security related portions of a system built by industry won't work since the government represents such a small portion of the overall market that the manufacturers may well decide not to sell to the government rather than accepting the limitations imposed by classification. This, in the end, might lead to a highly undesirable situation where private sector users (e.g., banks, insurance companies) have higher integrity systems than the government.

- But sensitive portions of systems and the known vulnerabilities that remain must be protected, in the interests of both the government and the manufacturers. It is quite likely therefore that the most sensitive portions of the government's analyses will be both classified and proprietary to the manufacturer. Careful, reasoned interaction between the government and industry will be needed to work out suitable working relationships.

- The Center will act in the interests and for the benefit of the Department of Defense and the Intelligence Community. Its evaluation will not be intended for use by other than the DoD. It will not make general product endorsements. But as with the Qualified Products List procedures (as prescribed in the DoD Defense Acquisition Regulations), the relative merit of a system in the hierarchy of evaluated products may be available publicly in order to provide incentive and encouragement for manufacturers to develop trusted systems and private sector users to employ them.

- Because of the wide range of sensitive environments that exist for information systems (ranging from privacy applications to compartmentation within the Intelligence Community, and from adjacent security levels (e.g., Secret and Top Secret) to full multi-level systems with Intelligence users and uncleared users), it will be vital for the Evaluated Products List to offer a range of technical categories and appropriate environments for specific systems. The approach of establishing levels of technical integrity which has evolved from the work of the Computer Security Initiative indicates the kinds of distinctions which will be made in evaluating systems. A range of suitable environments is possible with trusted systems because the security accreditation of ADP systems depends upon all of the aspects of the total system. The accreditation of a system to serve users cleared at both the Secret and the Top Secret level is not as difficult a problem as extending the use of such a system to uncleared users as well. The Department of Defense is now using Multics in such a limited environment serving both Secret and Top Secret cleared users. The Evaluated Products List should provide guidelines for implementing this type of operation where sufficient technical integrity of software products can be demonstrated. Finally, I would like to say that the establishment of an Evaluation Center, important as it is, must not be viewed as providing by itself the long sought answer to the computer security problem. Within the Department of Defense and the Intelligence Community, system builders

development of trusted system applications. The Services and Defense

will have to become aware of and properly employ the procedures for

Agencies are being encouraged to establish or enhance their own technical security test and evaluation capabilities to ensure widespread use and availability of trusted computer systems. The computer manufacturing community must work closely with the Center and these Service organizations to ensure that reasonable products are available for use in sensitive applications.

In conclusion, I would like to restate my awareness of the importance of this problem area, my enthusiasm for the establishment of the Evaluation Center, and my deep and continuing interest in its success. I encourage you participate fully in this Seminar, ask the tough questions, learn all you can and then go out and apply what you have learned so that we may all have trust worthy computers in the very near future.

#### INTRODUCTORY COMMENTS

#### STEPHEN T. WALKER

#### DIRECTOR INFORMATION SYSTEMS

#### OFFICE OF DEPUTY UNDER SECRETARY OF DEFENSE $(C^{3}I)$

Good Morning. It is indeed a pleasure to welcome you to the Fourth Seminar on the DoD Computer Security Initiative.

It was just three years ago that we began the Computer Security Initiative and just two years ago that we held the First Seminar here at NBS. We had two major goals when we started this effort and I am proud to announce that as of today I believe we have accomplished both of them.

As I described in my opening remarks at the last Seminar, our major <u>external</u> objective for the Initiative, that of getting the computer manufacturers involved in the development of trusted systems, had already come a long way as indicated by the five manufacturers who described their efforts at that seminar. This time, as you glance at your program you will see that we have eight manufacturers giving presentations; seven new ones including three European manufacturers and one giving an update from last time.

I must admit that I expected only two or three manufacturer presentations and as Pete Tasker and I were working out the program we had the pleasant task of frequently shuffling the program as more manufacturers accepted our invitation to speak.

I think it is obvious from the number and variety of manufacturers represented today and at the last Seminar that there is a strong interest in computer security and in trusted computer systems in the US and international computer manufacturing community. This external interest is most gratifying.

But just as exciting to me at least is the progress we have made to satisfy the major internal objective of the Initiative. At the last Seminar I hinted that within a year there would be a technical integrity evaluation process in being to serve the DoD.

In fact, as Admiral Inman has just announced, that goal has been met with the establishment of the DoD Computer Security Evaluation Center at NSA. The Deputy Secretary of Defense made it official as of January 1, 1981 and NSA has been hard at work pulling all the necessary pieces together to get the Center functioning. Tomorrow afternoon you will hear a status report on the Center from Mr. George Cotter of NSA.

I am personally very excited and pleased with our progress in just three years. It is clear to me that the time was right for what we have tried to do. My personal thanks to everyone who has helped make this possible. I believe that the combination of rapidly growing interest on the part of the computer manufacturers and the existence of a DoD evaluation capability will profoundly influence the integrity of computer systems in the very near term and from now on.

It is vital that we start to take advantage of this improvement as soon as possible. In just a minute, I would like to propose a challenge to both the computer manufacturers and the computer users both in this audience and beyond.

Let me first describe a particular situation as I see it in right now.

Over five years ago the Air Force, after extensive testing and evaluation, installed a Honeywell MULTICS System at the Data Services Center in the Pentagon. That system has successfully operated in a Top Secret environment with some users cleared only for Secret access for several years. It is a general purpose system being used for all kinds of programming and administration support to the AF.

I am not recommending that everyone go out and buy a MULTICS System to satisfy all their needs. But as I review the efforts of the many manufacturers that I have talked with lately, I realize that there is a real potential for a number of systems with integrity similar to MULTICS to be available in the not so distant future.

So what, you say! A Top Secret-Secret environment is not fully multilevel secure. I can't have the highest levels of sensitive data on my system with unclassified users so it hasn't solved my problem.

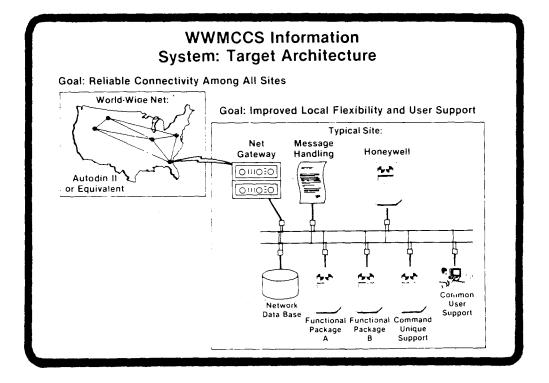

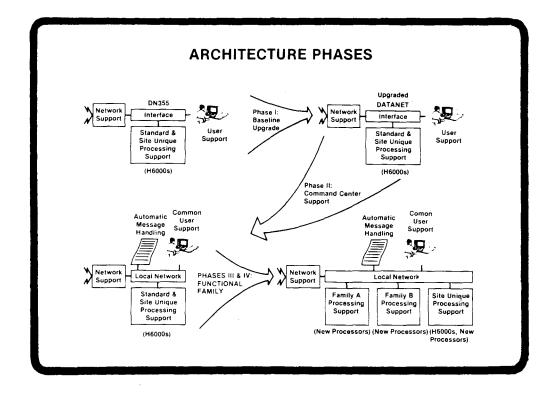

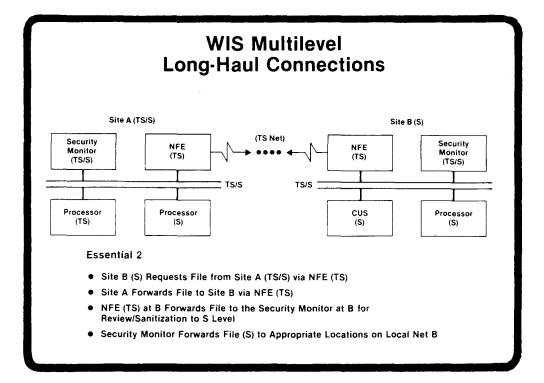

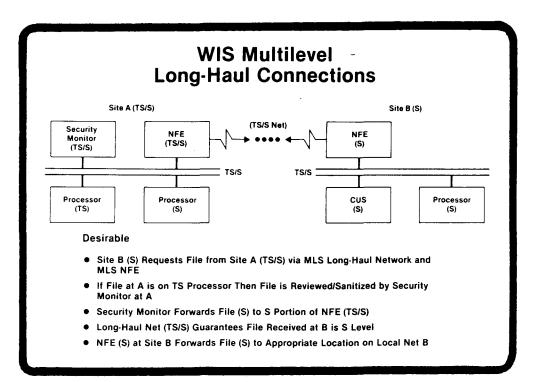

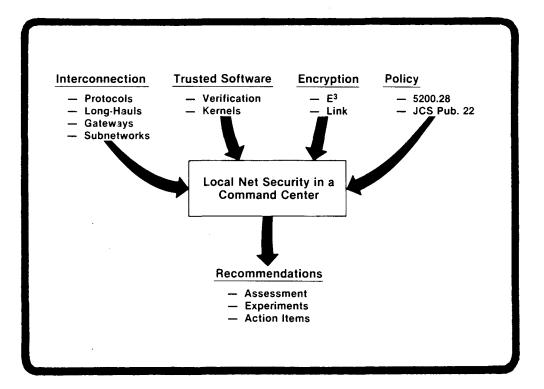

In reality though, not very many applications require a system to operate over anything like the full range of sensitive information. This afternoon you will hear about the computer security aspects of the WWMCCS Information System Modernization effort, perhaps the largest, highly sensitive computer system upgrade that the DoD will perform this decade. There are multilevel security problems throughout WIS but as you will hear, the requirements exist over a reasonable range of sensitivity levels, not necessarily over the full range of possible levels.

If one couples the fact that the manufacturers could soon develop trusted systems with integrity levels similar to MULTICS and the realization that many of our security requirements can be met by systems that operate over a limited range of sensitivity, it is possible to see how solutions to at least these limited applications may be forthcoming very soon.

You may accuse me of advocating a less then perfect solution by what I've just said. Far from that, though, I am advocating seeking a reasonable, useful solution prior to seeking the perfect solution. Indeed if we do not make serious attempts to crawl before we run here, we very likely will never get anywhere near that perfect solution. Now back to my challenge. I would like to challenge the users in this audience to seriously review their needs for trusted computer systems and determine, as Larry Bernosky has for the WWMCCS Information System, which needs could be met by systems able to operate over limited sensitivity ranges. To the extent that you can do this, I strongly urge you to convey this information to your local computer manufacturers representatives to help motivate them to develop systems to meet your needs, and then get involved in the evaluation of potential systems for your application.

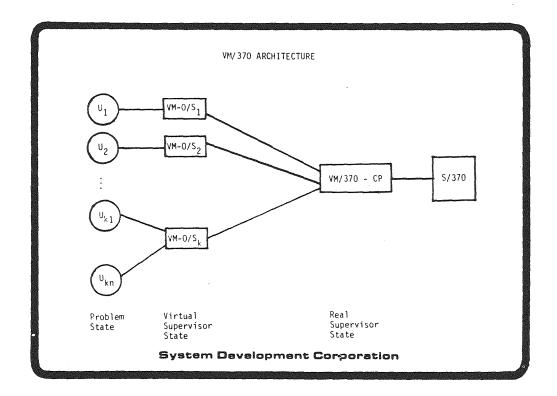

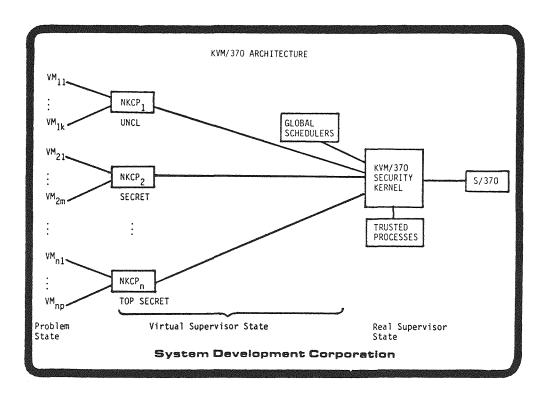

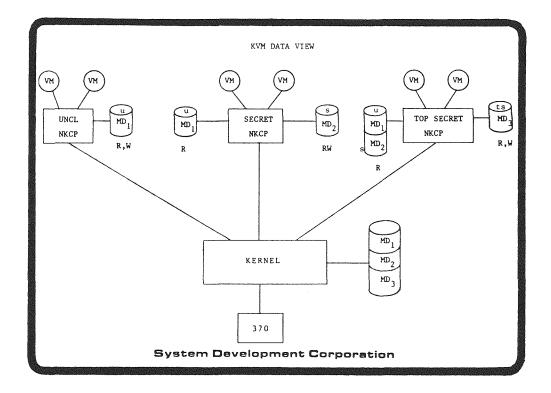

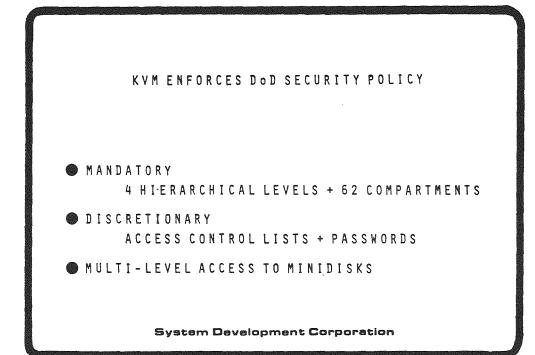

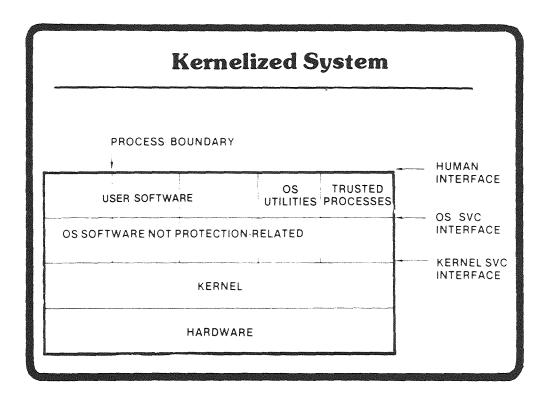

I would similarly challenge all the manufacturers in the audience to study what has been done to date, understand the security design of systems like MULTICS, Kernelized Secure Operating System (KSOS) and Kernelized VM 370 System (KVM) and incorporate these ideas into your product lines, quickly. More and more users are beginning to realize not only that they need improved integrity within their computer systems but also that it is possible to build systems with these improvements, and that they can begin to demand such features. As you can tell from the manufacturers participation here, at least some of your competitors are taking this seriously.

We've come a long way in the last few years. We've completed the first tough phase of the Initiative, getting the various pieces in place. Now it's time to move into phase two. This will involve a lot of work by the manufacturers and you the users have the opportunity and the responsibility to get involved.

I know by your being here that you are interested. I challenge you to get seriously involved.

I would now like to summarize the activities of the Initiative on the next few slides.

C-3

# DoD

# COMPUTER SECURITY INITIATIVE

# ...TO ACHIEVE THE WIDESPREAD AVAILABILITY OF TRUSTED COMPUTER SYSTEMS

Stephen T. Walker Chairman

DoD Computer Security Technical Consortium

# **COMPUTER SECURITY**

PHYSICAL SECURITY ADMINISTRATIVE SECURITY PERSONNEL SECURITY COMMUNICATIONS SECURITY EMANATIONS SECURITY HARDWARE/SOFTWARE SECURITY

# COMPUTER SECURITY INTIATIVE

TRUSTED: SUFFICIENT HARDWARE AND SOFTWARE INTEGRITY TO ALLOW SIMULTANEOUS USE AT MULTIPLE SECURITY/ SENSITIVITY LEVELS

WIDESPREAD: COMMERCIALLY SUPPORTED

|       | EVALUATED PRODUCTS LIST                                                                                                                  |                                            |                                         |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------|--|--|--|

| CLASS | TECHNICAL<br>FEATURES                                                                                                                    | EXAMPLES                                   | POSSIBLE<br>ENVIRONMENTS                |  |  |  |

| 1     | -                                                                                                                                        | MOST COMMERCIAL<br>SYSTEMS                 | DEDICATED MODE                          |  |  |  |

| 2     | FUNCTIONAL SPECIFICATION<br>REASONABLE PENETRATION<br>RESULTS                                                                            | "MATURE"<br>"ENHANCED"<br>OPERATING SYSTEM | BENIGN, NEED TO<br>KNOW<br>ENVIRONMENTS |  |  |  |

| 3     | REASONABLE MODERN<br>PROGRAMMING TECHNIQUES<br>LIMITED SYSTEM INTEGRITY<br>MEASURES                                                      | MULTICS                                    | AF DATA SERVICE<br>CENTER TS-S          |  |  |  |

| 4     | FORMAL DESIGN<br>SPECIFICATIONS SYSTEM<br>INTEGRITY MEASURES                                                                             |                                            | NO USER<br>PROGRAMMING<br>TS-S-C        |  |  |  |

| 5     | PROVEN DESIGN<br>SPECIFICATIONS VERIFIABLE<br>IMPLEMENTATION LIMITED<br>COVERT PATH PROVISIONS                                           | KSOS<br>KVM                                | LIMITED USER<br>PROGRAMMING<br>TS-S-C   |  |  |  |

| 6     | VERIFIED IMPLEMENTATION<br>AUTOMATED TEST<br>GENERATION EXTENDED<br>COVERT PATH PROVISIONS<br>REASONABLE DENIAL OF<br>SERVICE PROVISIONS |                                            | FULL USER<br>PROGRAMMING<br>TS-S-C      |  |  |  |

|       | ·                                                                                                                                        |                                            |                                         |  |  |  |

э

## **COMPUTER SECURITY INITIATIVE**

ON JANUARY 1, 1981 THE SECRETARY OF DEFENSE ASSIGNED RESPONSIBILITY FOR COMPUTER SECURITY EVALUATION FOR DOD TO THE DIRECTOR, NATIONAL SECURITY AGENCY.

# COMPUTER SECURITY EVALUATION CENTER

ESTABLISH TECHNICAL EVALUATION CRITERIA

EVALUATE INDUSTRY AND DOD SYSTEMS

MAINTAIN EVALUATED PRODUCTS LIST

SPONSOR R&D IN COMPUTER SECURITY

ENCOURAGE DEVELOPMENT AND WIDESPREAD USE OF TRUSTED COMPUTER SYSTEMS

# CURRENT INITIATIVE EVALUATION EFFORTS

CONTROL DATA

DIGITAL EQUIPMENT CORPORATION HONEYWELL

INTEL

TYMSHARE

UNIVAC

# UNDER DISCUSSION

**BURROUGHS**

FEDERAL AND SPECIAL SYSTEMS GROUP

CHRIS TOMLINSON

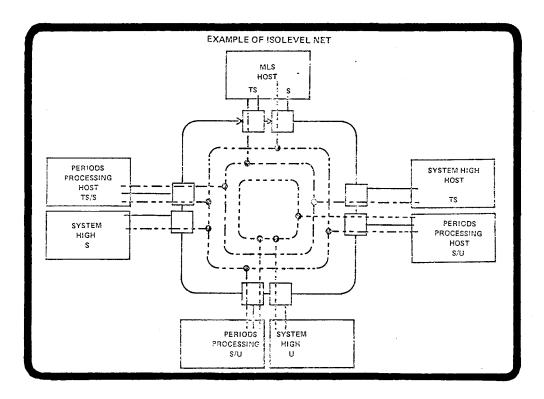

#### **RESEARCH AND DEVELOPMENT**

- SYSTEM HIGH

- ▶ PERIODS PROCESSING

- ▶ MLS HOSTS

USING LOCAL NETWORK TECHNOLOGY

### **ISO-LEVEL POLICY**

COMMUNICATION IS PERMITTED ONLY AMONG SUBSCRIBERS AT THE IDENTICAL SECURITY LEVEL (CLASSIFICATION, CATEGORY)

NO OTHER COMMUNICATION CAN

D-3

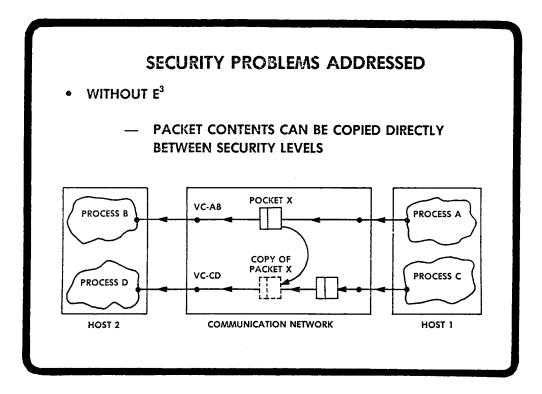

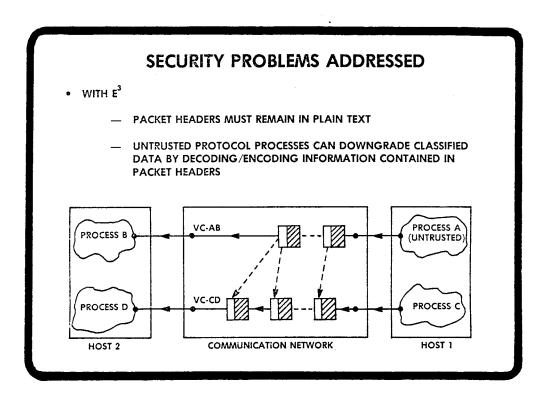

### POTENTIAL SOLUTIONS

#### STORAGE CHANNELS

- ELIMINATE VARIABLES

- ADDRESSES

- LENGTH

- OTHER HEADER FIELDS

- ENSURE THAT UNTRUSTED NETWORK PROCESSES CANNOT COMMUNICATE WITH ONE ANOTHER OUTSIDE THE POLICY

TIMING CHANNELS

TIME DIVISION MULTIPLEXING

×.

#### CR80-A Fault Tolerant Computer for Implementation in Secure Systems

### Asbjørn Smitt Head of Research and Development Christian Rovsing A/S, Ballerup, Denmark

#### 1.1 General

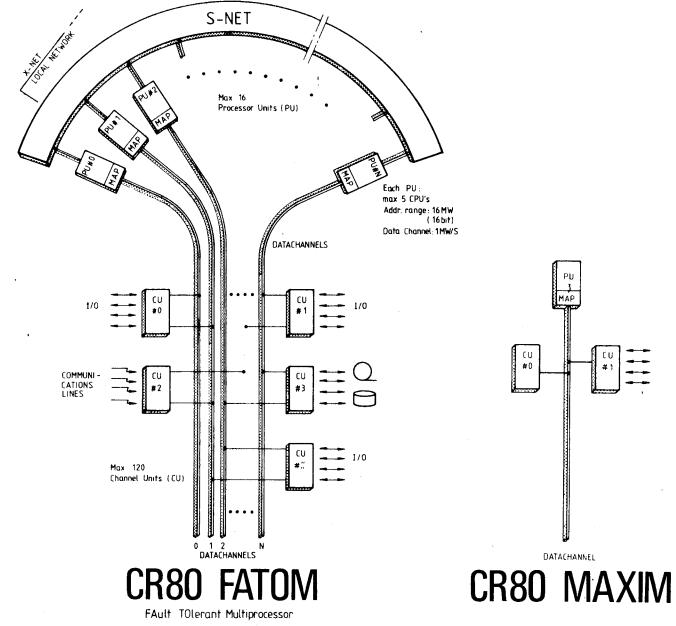

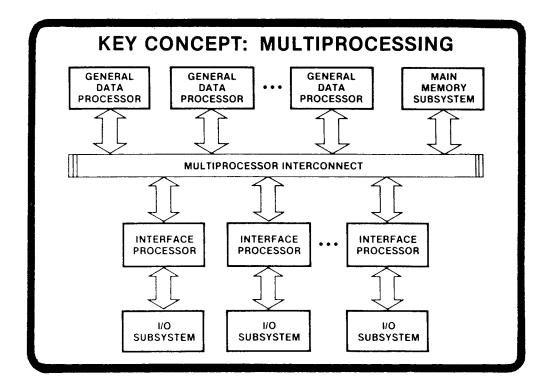

Christian Rovsing A/S with the CR80 MAXIM and FATOM virtual machines has introduced a new and powerful architecture for implementing secure systems on a ultra-reliable, easy to maintain and modular fail safe computer. The high speed memory mapped multiprocessor computers have been designed to provide modular growth in processing power and memory requirements to cope economically with the requirements of:

- General purpose computer systems

- Packet switches

- Message switches

- Control and Command Information

- Concentrators

- On-line systems

- Terminal systems

- Front end processors

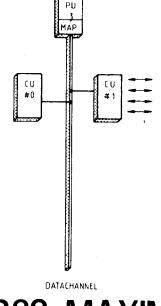

The illustration overleaf shows that the CR80 FATOM computer tightly couples up to 16 Processing Units (Multiprocessors) together via the S-NET, and that each peripheral connects through individual channels to two Processing Units, one channel being the active connection for a connected peripheral, the other the back-up connection. Also it is seen that the CR80 MAXIM (Memory mapped Maxi-computer) is the single Processor Unit, non-redundant subset of the CR80 FATOM (Fault Tolerant multiprocessor) otherwise they have identical high performance characteristics.

The CR80 FATOM fault tolerant computer differs from other computers (large, medium or small) in that it, based on a unique distribution of its memory providing nearby unlimited processing power, up to 50 Million instructions per second (MIPS) together with minimum added hardware to achieve its "self repair" features and 256 Mega word maximum memory size.

E-2

Extensive hardware checks has been incorporated throughout the CR80 architecture, supporting integrity and security in execution of both application and system programs, ensuring that erroneous interaction among users, and with the system software, are prohibited. This is extremely important during software maintenance and development, once a fault tolerant system has been brought operational, as well as facilitating the initial software development and debugging.

The CR80 architecture and DAMOS system software supports modularily the total spectrum of virtual memory machines, from the 0.7-3.0 MIPS MAXIM multiprocessor computer with one or more CPUs, up to the 50 MIPS, N+1 redundant FATOM computer, incorporating the cost effective approach of only having 1 single spare unit, capable of backing up for any of N working units). The CR80 can be upgraded in the field, often without stopping operational use, due to its on-line maintenability and unique galvanic isolation between system elements at the card-magazine level.

A CR80 Processor Unit (PU) constitutes either a uni- or multiprocessor computer with from 1 to 5 CPUs (.7 to 3 MIPS). The CR80 FATOM connects up to 16 Processor Units (PUs) together via the extremely fast S-NET (up to 512 Mbit/sec.) into a tightly coupled multicomputer with up to 50 MIPS capability. In addition all lower levels of input/output processing is distributed to the I/O controllers (peripheral processors) in the Channel Units (CU), this further enhances the CR80 above the simple accumulated processing power of the CPUs.

The I/O Controllers (peripheral processors) communicates with PUs through one port of the triple ported controller memory, the two other ports allowing for this memory being part of the address space of two processing units (PUs), which ensure an alternative path, in case of a Processing Unit (PU) failure. The CR80 computers also gain their strength from very fast intelligent multiplexed Direct Memory Access (DMA) channels between the distributed memory in PUs and CUs and that the imbedded channel processors (S-NET & DATA CHANNEL) with minimum interruption of the CPUs autonomeously handle and ensure the integrity of hundreds of simultaneous active logical channels between programs and processes.

The CR80 FATOM basic system philosophy is to achieve N+1 redundancy on all levels, both processors and I/O controllers. A unified system approach to software in a redundant system, relieving application software as far as possible of mechanisms and functions necessary for fault tolerance, moving these to the system S/W. The CR80 FATOM Computer thus is designed to have no single points of failure on a system basis, this includes all parts of the system: Processors, busses, I/O devices, power supply, cooling and software in order to achieve a continously available no-break computer. The on-line maintenance features, allows any failed module to be exchanged and tested, without interrupting system operation.

Also the CR80 modular packaging and integration system, ensures the capability for expansion of a CR80 FATOM Computer to virtually any physical size, using only a few standard types of modules and cables, as well as achieves the cost efficiency of both the single and fault tolerant CR80 Computers.

12

1.00

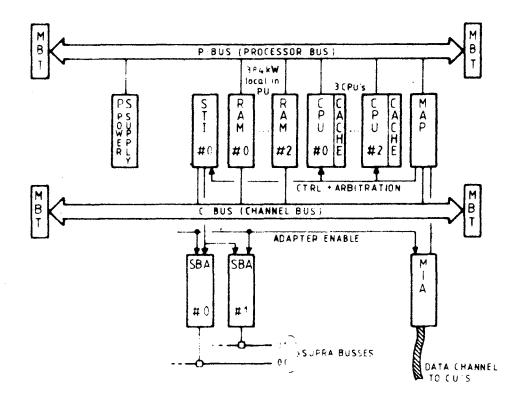

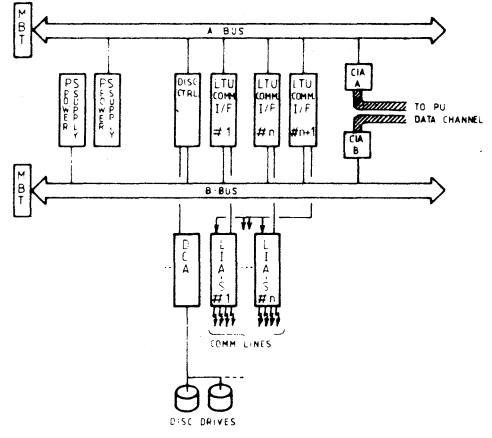

#### PU Logical Organisation

As an introduction to the features of the CR80 memory mapped PU a brief discussion of the CR80 Processor Unit Logical Organization, shown overleaf is given.

Interconnection of the PU modules is performed by means of two parallel transfer busses, the (Processor Bus) and the (Channel Bus) implemented as two backplane printed circuit boards. The busses have identical electrical and timing specifications with the following characteristics: transfer rate up to 4 mega word per second (16 bits + 2 parity bits), addressing of 1 mega word as word or byte. The Processor Bus performs as transfer bus for the Central Processor Units (CPUs), while the Channel Bus performs as transfer bus for the Channel Bus modules (DMAs).

The central processor units, CPUs, are general purpose processor units with a word length of 16 bits and the ability to address 64K word of instruction and 64K word of data. All data/instruction transfer performed by the CPU are via the processor bus and the memory MAP to the memory. Physically, the CPUs and the memory MAP are connected to the same Processor Bus, but logically the CPUs recognize the MAP as being located between the memory and the CPU.

The function performed by the memory MAP is to expand the addressable memory area to 16 mega word of which 1 mega word can be located in the PU as fast access, local storage, while the remaining 15 mega word can be located on the data channel. Besides the address translation, the MAP also includes memory read/write protection, the protection can be performed individually for each 1K page of the memory.

E-5

CR80 FATOM PU CONFIGURATION

CR80 FATOM CU CONFIGURATION

The functions performed by the MAP on the Processor Bus transfers are also performed on all Channel Bus transfers, meaning the Channel Bus Modules can access the complete 16 mega word memory area, but only the areas which are not protected.

Beside the address translation described above, the MAP module also includes the Channel direct memory access (DMA) function, interrupt preprocessing and Data Channel Interface.

The DMA is used for blook transfer between shared memory with peripheral Controllers and PU local memory and is under control of the Input/output system software.

The interrupt preprocessing performed ensures that only interrupts (CPU or I/O) with sufficient priority will cause a context switch in one of the CPUs, while all other interrupts will be queued by the MAP, until the CPU status allows service of them.

Transfer on the Data Channel will be performed by the memory MAP when the addressed location is not within the PU Local Main Memory addressing space (I Mw).

Security is supported by means of memory access protection and division of instructions into three privilege classes.

The CPU has 16 states of which one (state  $\emptyset$ ) is a user state and 15 (states 1 through 15) are system states. In user state only not privileged instructions may be executed. Medium privileged instructions can be executed at all system states while the most privileged instructions are reserved for execution at system state 15.

Attempt to illegally execute a privileged instruction in user state or system states 1 through 14 causes a local interrupt, upon which the CPU automatically envokes a supervisor routine.

E-7

The CPU state is changed by means of the MON\_instruction which is used to activate system procedures.

#### 1.3. CR80 Security Mechanisms

The inherent logical and physical separation of programs and data in the CR80 architecture is well suited for preventing unauthorized access to data and programs and for preventing non-intended modification of programs.

The objectives of the protection mechanisms in the CR80 are:

- to protect data belonging to a process against unauthorized modification

by other processes and against not intended reading;

- to protect programs against modifications, and,

- to prevent unauthorized execution of programs and system resources

- to prevent processes from monopolizing the processor.

Security is supported by means of memory access protection and division of instructions into three privilege classes.

The CPU has 16 states of which one (state  $\emptyset$ ) is a User state and 15 (states 1 through 15) are System States.

Higher states have more privileges than lower states. In user state only not privileged instructions may be executed. Medium privileged instructions can be executed at all system states while the most privileged instructions are reserved for execution at system state 15.

Attempt to illegally execute a privileged instruction in user state or system states 1 through 14 causes a local interrupt, upon which the CPU automatically envokes a supervisor routine.

The CPU state is changed by means of the MON\_instruction which is used to activate system procedures.

In addition to the memory protection provided in USER STATE by the MEMORY MAP, each of the system states has its own memory bound register. Only data memory locations below or equal to this boundary value may be modified while all data memory locations available might be read in SYSTEM STATE.

The Memory Map protection mechanism which is active in user state is implemented by means of two access control bits for each 1 Kw page in memory. The protection values are:

access control bits:

- 00 Page absent

- 01 Full access

- 10 Read only

- 11 No access

As will be seen in the following all non-privileged (USER STATE) memory accesses (both from CPU's and DMA's) go through the Memory Map, and are checked by hardware not to violate the protection value. In the system state full access (read or write) is granted irrespective of the protection value.

If a not allowed access is attempted, the transfer is terminated without sending the physical address to the memory, and, a transfer error is signalled from the Memory Map.

The "Page absent" condition is used to invoke the demand paging feature of DAMOS. It indicates that the accessed page is not resident in main memory (or not mapped in), and will lead to suspension of the process until the page has been loaded into memory or relocated.

E-10

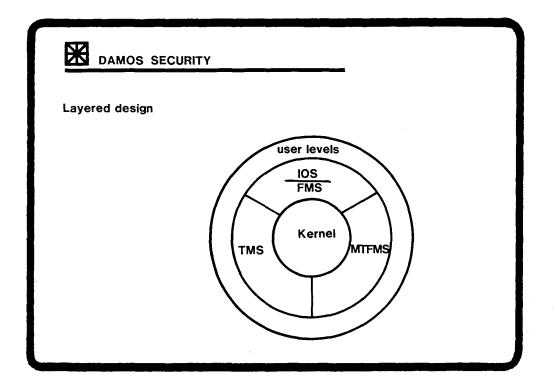

#### 1.4 Security

The CR80 operating system DAMOS offers comprehensive data security features. A multilevel security system ensures that protected data is not disclosed to unauthorized users and that protected data is not modified by unauthorized users.

All memory allocatable for multiple users is erased prior to allocation in case of reload, change of mode, etc. The erase facility is controlled during system generation.

DAMOS is specified using the formal notation of the Wienna development method with the intention of making formal verification possible.

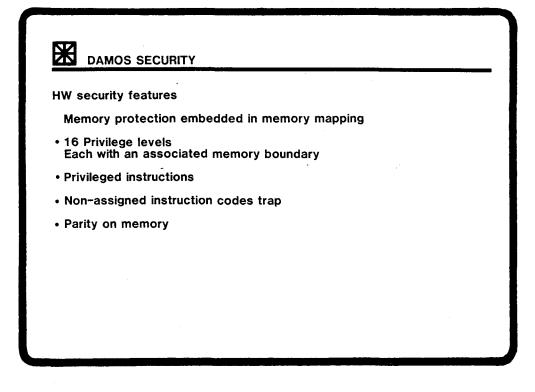

The security system is based on the following facilities:

- a. Hardware supported user mode/privileged mode with 16 privilege levels. Priviliged instructions can be executed only when processing under DAMOS control.

- b. Hardware protected addressing boundaries for each process.

- c. Non-assigned instructions will cause a trap.

- d. Primary memory is parity protected.

- e. Memory bound violation, non-assigned instructions, or illegal use of privileged instructions cause an interrupt of highest priority.

- f. The hierarchical structure of DAMOS ensures a controlled use of DAMOS functions.

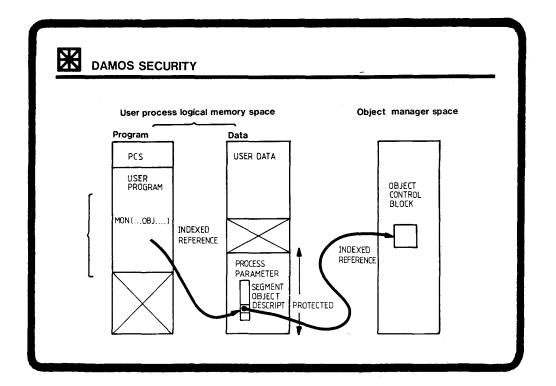

- h. A general centralized addressing mechanism is used whenever objects external to a user process are referred to.

- i. A general centralized access authorization mechanism is employed.

Centralized addressing capabilities and access authorization are integral parts of the security implementation. User processes are capable of addressing Kernel objects only via the associated object descriptor table. The following types of DAMOS objects are known only via object descriptors:

- a. Processes

- b. Synchronization elements

- c. Segments

- d. Devices

- e. PUs

- f. CPUs

- g. Ports

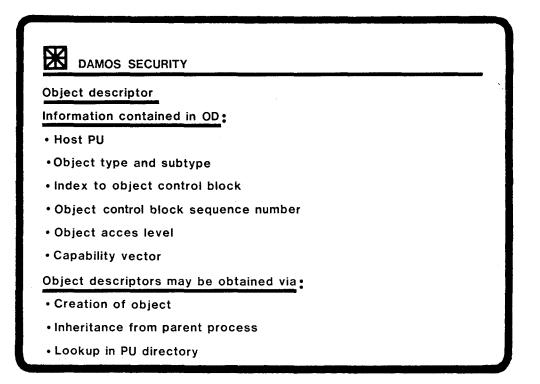

The object descriptor forms the user level representation of a DAMOS Kernel object. It contains the information necessary for the Kernel to locate its low level representation and to ensure its security and integrity:

- a. Host PU

- b. Object type

- c. Object control block index for use by the Kernel to locate the corresponding object control block.

- d. A sequence number which must match a number in the object control block (to prevent reallocated blocks from being erroneously accessed).

- e. A capability vector specifying the operations which may be perfor med on the object by the process which has the object descriptor.

The access right information concerning the various DAMOS objects is retained in a PU directory of object control blocks. Each control is associated with a single object.

When the access right of a process to a segment is verified and the segment is included in the logical memory space of the process, the contents of that segment may be accessed on a 16-bit word basis at the hardware level subject to hardware access checks.

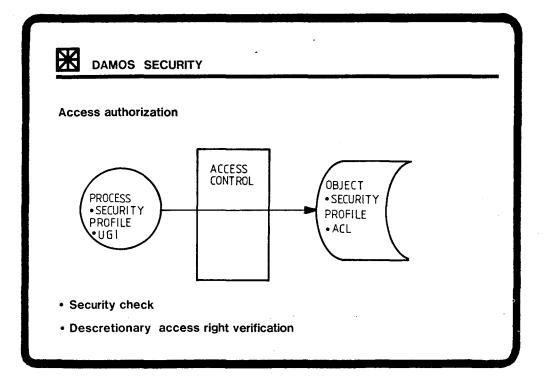

Authorization of access to an object is based on

- a general security policy, and

- a discretionary access checking

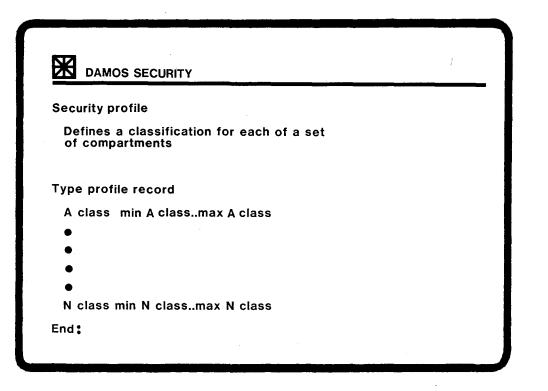

The security policy is based on a multilevel -multicompartment security system.

Objects are associated with a security classification level for each compartkent (i.e., set of data with the same kind of information) and subjects (processes) are associated with a security clearance level for each compartment. Both entities are described in a common type:

• the security profile

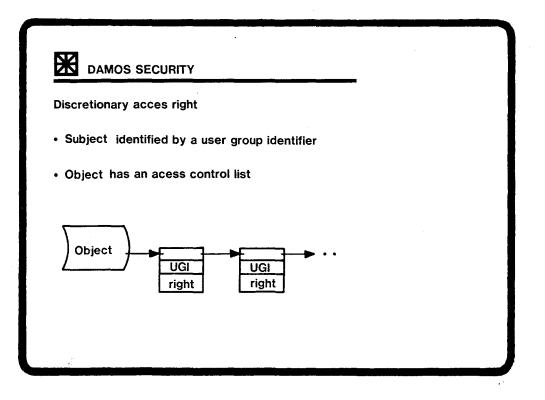

Discretionary access checking is based on

- identification of access classes of subjects (processes), and

- statements of access capabilities for explicitly enumerated access classes of subjects vis a vis a given object.

Access to an object is authorized if the following conditions are both fulfilled:

- the access operation requested is allowed according to the capability vector in the object descriptor

- the combination of process security profile, object security profile and operation (read or write) agrees with the security policy.

The security policy is:

- A process may read from objects with classification not higher than that of the process. An untrusted process may write to objects with classification not lower than that of the subject.

- A trusted process may write to objects with any classification.

A process can only obtain access rights (i.e., an object descriptor) to a DAMOS object in the following ways:

- a. By inheritance from a parent process

- b. By creating the object.

- c. By successful look-up in the PU directory.

Similarly, a process can only distribute access rights to objects registered in its object descriptor table. This may be done:

- a. By inheritance when creating a child process

- b. By entering the object into the PU directory by a symbolic name.

When an object is entered into the directory it is specified by whom it may be looked up and what capabilities they should have vis a vis the object.

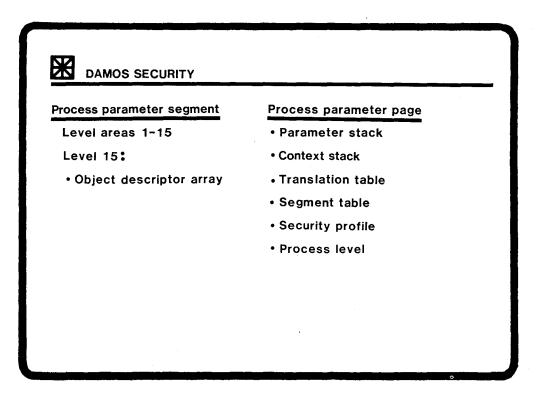

The object descriptor table and Security profile of a process is kept in a memory which is accessible by that process when it is executing in privileged mode, but protected against modification by the process when executing in user mode.

#

#### Kernel

- Directory functions

- CPU management

- Process management

- Memory management

- Inter process communication

- Device management

- Device handlers

- •Error processing

- •Real time clock

- PU management

- PU service module

- •Transfer module

- Basic transport service

## DAMOS SECURITY

#### Objects

Security is based on controlled acces to objects

----

#### Kernel objects

- PUS

- CPUS

- Processes

- Synchronization elements

- Virtual memory segments

- Devices

- Communication ports

### Objects Magnetic tape file management system File management objects • Devices (disk drives) Devices (tape decks) • Volumes (disk packs) Volumes (tapes) Files • Files • Users Users Terminal management objects • Devices (communication controllers) Lines • Units (terminal, LP, VC,) •Users

##

#### Security check

- A process may read from objects with a classification not higher than that of the process

- •A process may write to objects with a classification not lower than that of the process

- •A trusted process may write to objects with any classification

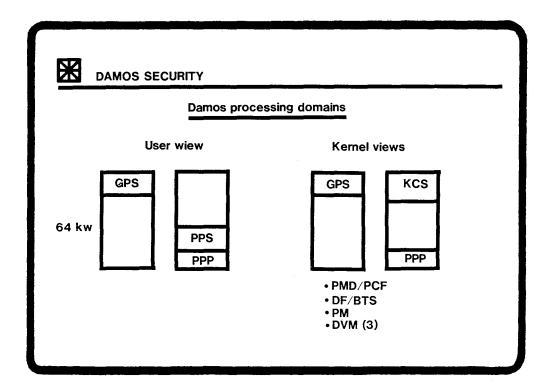

| hange of execution level<br>MON instruction<br>RTM instruction<br>Interrupt<br>RTI | Change of view (proce<br>• CALL instruction<br>• RET instruction<br>• Interrupt<br>• RTI | essing domain)<br>Only at level 15 |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------|

|                                                                                    | · ·                                                                                      |                                    |

#### Computer Security and Control Data

#### Terry A. Cureton Program Manager, Security Systems Control Data Corporation

August 10, 1981

[SLIDE: CDC Logo]

It is a pleasure for me to represent Control Data at this seminar. We have been observing the activities of the DoD Computer Security Initiative for some time, and are impressed with your progress. Until recently, our participation in the Initiative has been silent. For the most part, this has been due to the largely theoretical or experimental nature of the material presented. However, the Initiative has given us an opportunity to look at our own experiences in computer security from another viewpoint. We can now see the parallels and principles common to both the theoretical work and our experience as practitioners of computer security. The message we would like to share with you today is that we at last see a convergence between the theory and practice.

[SLIDE: Topics]

To begin, I must start with what Control Data is, and why we are involved in computer security. Then, I would like to dispel a myth about security and performance, by relating that to our unique machine architecture. Next, I will briefly describe how that architecture is reflected in our operating system design. A comparison of commercial versus government security requirements will show how we plan to meet both. Another comparison of formal and informal design methodologies will show how we think they are converging. Lastly, I will describe our involvement with the DoD Initiative and our view of its impact on the industry as a whole.

[SLIDE: Control Data Reputation]

What kind of company is Control Data?

- Many of you know Control Data is in the large-scale scientific and engineering computer business.

- That is our tradition and our legacy, since the company was founded in 1957 since the days of the 1604 and the 6600.

August 10, 1981

[SLIDE: Control Data Today]

But you may not be aware of the range of Control Data's business today. Yes, we still make super-scale computers for our systems business, but we are also the industry's leading supplier of peripherals - both OEM and plug-compatibles, in addition to our own label. The next time you walk into a room full of disks, there's a good chance (65%) that we made them, since we supply OEM peripherals to all but one of the major manufacturers. We are also deeply committed to education with our unique PLATO system. PLATO is winning acceptance in uses ranging from teaching grade school fundamentals, to training airline pilots and nuclear safety engineers. But it is in Data Services that we are the world-wide leader.

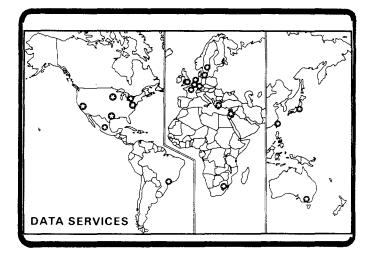

[SLIDE: DATA SERVICES]

Our Data Services Company operates both commercial and scientific data centers around the world, around the clock. Its a more than half billion dollar business, reaching from Main Street to Wall Street. And - whether it is a small businessman dealing with our Service Bureau Company in Cleveland - or an engineering firm dealing with our CYBERNET Services in Copenhagen - the two questions we always get are:

[SLIDE: DS Customers Ask]

"How much will it cost?" and "How secure will my data be?".

[SLIDE: Security (1)]

Clearly, security is a customer concern, and for Control Data it is a hard-nosed, hard-headed business need. It is here that Control Data learned about conputer security in a day-to-day pragmatic way. We have been addressing that need for more than 20 years, since the beginnings of Data Services.

Now, Data Services is a large chunk of our business, in fact they are our largest Systems "customer". Their needs have a major impact on system design and development. Simply put - <u>Security</u> has been <u>essential</u> to our largest systems marketplace for more than 20 years. That's why Control Data has been involved in computer security. We will have to look at the data services environment to see <u>how</u> it relates to computer security.

[SLIDE. Timesharing Environment]

From a security viewpoint, it is the timesharing environment where the needs are greatest. The first need of course, is to simply keep it running, since users have little patience for system downtime. That requires a good deal of system integrity, in the first place. By definition, timesharing means multiple users sharing system resources. Those resources and the users' data are real and tangible assets which must be protected. Then, resources have to be controlled so that all may share equitably, and if you want to get paid, they have to be accounted for. Finally, users have to be kept seperate, since they might be competitors.

Control Data met those needs by developing a system specifically designed for the timesharing environment. Over time, security flaws were discovered and corrected, and new security mechanisms evolved into the system design. We built up a great deal of <u>practical</u> experience with that system, and that system evolved into our standard system of today. But it wasn't until the DoD Initiative that we fully recognized the unique advantages of the CYBER 170 architecture regarding security.

What is so unique about the CYBER 170 architecture and security? The answer in a word is - <u>Performance</u>. There seems to be a growing supposition in the industry, that security can only be obtained at the expense of performance. We would like to dispel that myth, by showing how the CYBER architecture and hardware can provide security without penalizing performance. To understand why, we have to first examine the relationship between security and performance, and then how that relates to design.

#### [SLIDE: Performance]

When considered in a broad sense, performance over the long term requires both speed and endurance - that's why the Indianapolis 500 is so tough. It isn't worth much to be the fastest in the race, if you can't keep it running long enough to finish. In computing terms, endurance is a combination of reliable hardware and software, and the total system's ability to recover when something does break.

#### [SLIDE: Security (2)]

In that sense, the concept of integrity as a security requirement, is just another way of describing endurance for performance. Thus the emphasis on system integrity, as described in these DoD Seminars, is consonant with our experience in computer security. That's one sign of a convergence between the theory and practice.

Given that endurance and integrity are just different views of the same set of requirements, then those hardware and software features which contribute to the <u>endurance</u> of a system are, in fact, contributing to <u>both</u> performance and security. Here's another way to look at it.

August 10, 1981

[SLIDE: Implementation]

From this viewpoint, we can see how security and performance should be mutually benefical - synergistic if you will - rather than conflicting goals. How these features are implemented, - and which are in hardware - is where conflicts arise. If security features must be implemented in software - at the expense of performance, - then the software designer is forced to make a tradeoff decision. Historically, the choice has been in favor of performance, simply because that's what sold computers. But that tradeoff is beginning to shift the other way now.

[SLIDE: Hardware Security/Performance]

Specifically, there are four key hardware characteristics which are contribute to both performance and security:

o Machine Architecture,

o Memory Protection,

- o Context Switching, and

- o Reliability Features.

Let's look at each, beginning with the architecture.

[SLIDE: Architecture]

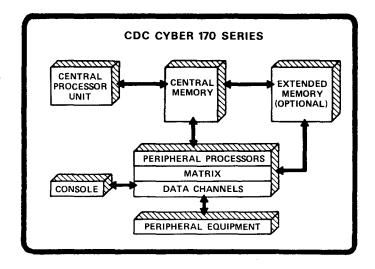

This is the general architecture of the Control Data Cyber 170 series computers. What is unique in this block diagram is the Peripheral Processor Units (PPUs) in the middle. These are up to 20 separate, independent computers, which operate concurrently with, but independent of, the Central Processor. Note also that all I/O operations must be performed by the PPUs. Already we see the principle of separation of functions implemented in hardware. I'll come back to the performance aspects of this later. Let's just see how that architecture is reflected in the system design.

[SLIDE: System Layout]

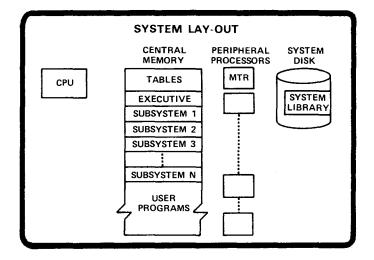

I must explain that only system software executes in the PPUs. In fact, most of the operating system consists of modules to be executed in a peripheral processor. The PPUs also have primary control of the operating system. The one at the top, labeled MTR (Monitor) is the real boss of the system. The executive shown in central memory is just a fast assistant to MTR. User jobs also reside in central memory and only execute in the CPU. Again, we see a separation of functions. When a user program requests I/O, or other services, from a PPU, it validates the request and performs the operation completely independent of the CPU. The CPU program is thus isolated from I/O operations and cannot directly participate in error handling and so

August 10, 1981

on.

On performance, it should be noted that concurrent operations in the PPUs also means that the software designer need not make a tradeoff between security and performance. While a PPU module is laboriously checking parameters or validating a user's authority to perform an I/O function, the CPU can be producing useful computations for another user. This hardware separation pays off directly in performance, and at the same time, establishes a solid base for security.

Let's move on to memory protection. Actually, memory protection also starts with the architecture. What better isolation can there be than between physically separate memories? Each Peripheral Processor has its own independent memory, separate from the other PPUs, and more important - from Central Memory where users must reside. Again, hardware design provides the separation and isolation necessary for security.

But notice, there are some system tables and software sharing central memory with the user jobs. Here separation is maintained by the CPU memory protection scheme.

#### [SLIDE: Memory Protection]

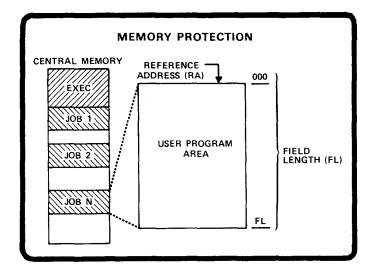

This scheme is simply a base and bounds hardware register pair. The Reference Address (RA) is the starting address of memory assigned to an executing program. The Field Length (FL) is the length of that area. These hardware registers are part of the CPU, but are not accessible to the executing program. Their use is completely transparent. To the user, all memory addresses are relative to assigned memory and the hardware precludes any other access. Thus the CPU program does not handle real memory addresses, which is one characteristic in common with virtual memory systems. This eliminates user participation — or observance — of memory management. Since only the Reference Address changes when a program is moved or reloaded into memory, usage can be highly dynamic and efficient. Doing it entirely in hardware provides even greater efficency, due to the simplicity of the mechanism. Here we see both security and performance as a result of how memory protection is implemented.

#### [SLIDE: User/System Interface]

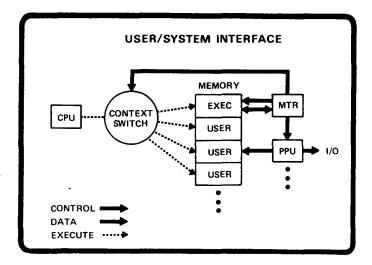

Another critical security/performance concern is the need for safe and fast context switching between programs. The actual context switching mechanism is provided by a hardware feature, which has been characterized as the "ultimate interrupt" but officially known as the Exchange Jump operation.

An Exchange Jump can be triggered by either a PPU or a CPU instruction. This single instruction stores the complete set of CPU registers, including RA and FL, into memory and reloads them from the same memory block. Yes, it sounds like magic, but it does go both ways in the same operation. The result is a complete two-way swap of

August 10, 1981

- the execution state of the current CPU program - with the memory image of the state of another program. The whole thing is transparent to the program and the hardware insures that nothing is lost -  $\underline{or}$  gained - in the exchange.

The exchange operation is <u>very fast</u>. For comparison, it is roughly the same time as a floating point divide operation. In some processor models it is even faster. In that case, it could be said that "a <u>swap</u> is faster than a <u>FLOP</u>." Again the intent was performance, but the result is security since it is implemented in the hardware.

A CPU triggered exchange is part of the normal user/system interface. In this case the user program merely relinquishes the CPU to the operating system. On completion of the request, the CPU is returned in a similar manner.

The system PPU monitor however, can independently trigger a context switch at any time. This is how a PPU module can both monitor and control the time-slicing of the CPU among many jobs. It is also the mechanism for "pulling the plug" on programs consuming too much of a resource or hung up, and becoming a "denial of service" threat to others. It effectively eliminates of any form of user lockup, as the PPUs always have the ultimate control. Thus a hardware context switching capability can provide not only performance and security but resource control as well.

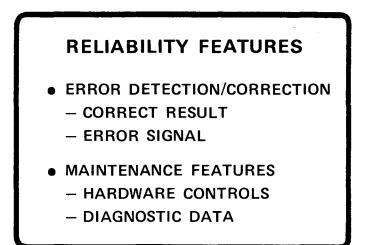

#### [SLIDE: Reliability Features]

Finally, we come to those reliability features usually thought to be interesting only to engineers. Error detection and correction features are the most basic elements of hardware integrity. An adequate set insures that the hardware will yield just two results either a correct result, or a signal that it cannot perform the function properly. In addition, the diagnostic data produced by these and other maintenance controls contribute to long term stability, reliability and recoverability. My point is that they are not to be overlooked when considering security. We are all aware that most system flaws are exposed when operating in crisis mode - usually in response to an error.

[SLIDE: Hardware Security/Performance (Result)]

In short, there are four key hardware characteristics which contribute heavily to both performance and security:

- o Machine Architecture

- o Memory Protection

- o Context Switching

- o Reliability Features

All of these establish the base on which software must rely, to provide both security and performance in the broad sense.

#### [SLIDE: Network Operating System]

At this point I should introduce you to our Network Operating System, (N.O.S. or NOS as you will). The name makes it clear that NOS is network oriented. It not only supports access via communications networks, but also supports multi computer networks both locally and remotely. NOS is a multi mode system offering a full range of processing modes including local and remote batch, database managers and transaction processing, and a variety of interactive programming environments. Obviously it is a multi user system as well, and that's where security becomes a key requirement.

-

#### [SLIDE: NOS Characteristics]

One of the outstanding characteristics of NOS is that it is a capabilities based system. It all begins with the built-in concept of individual users. Each user must be known to the system, and their capabilities defined on an individual basis. From this is built an accounting system where every activity in the system is attributable and traceable to a user. Users are totally isolated from each other, and the operating system. NOS relies heavily on the hardware separation and memory protection features for this isolation. For NOS users, the only means of sharing data is via the file system. The file system is built around individual ownership of files, and access is, - by default - restricted to the owner. If the owner chooses, other users' access to a file may be specified on the basis of user identity and mode of access. NOS has file passwords too, but they are seldom used since they are independent of identification.

Interestingly, the file system carries the memory addressing concept much further, and exhibits most of the characteristics of a virtual memory system. Space allocation is dynamic, on an as-needed basis, and does not require pre-allocation. That makes it very spaceefficient and avoids deadlocks. All I/O references are relative to the logical file name, and the system (a PPU module) does the mapping to real device addresses. Thus, NOS can preclude access outside of a file, and to unwritten space.

Users and their files are also grouped into higher level FAMILYs with no access to files across FAMILY groups. This is particularily valuable in a university environment, to separate students from faculty. Families are then divided into sub-families by storage device to provide further physical separations. The result is that a population of NOS users can be easily managed dynamically and without inconvienence to the user. Both Families and Sub-Families may be controlled as a group via operator commands.

In summary, NOS benefits from both a solid hardware security base, and a design intended for commercial timesharing, which has withstood the test of time and emerged robustly healthy.

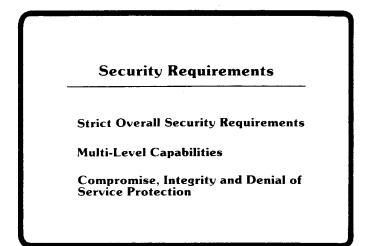

[SLIDE: Security Requirements (1 of 2)]

But what of the DoD's security requirements? Although the words may differ, there is a strong similiarity between commercial and government security requirements. When you speak of a kernelized system, it must be as simple a possible - to allow provability - and by definition must be modular. It would be interesting to compare this concept to our system PPU modules. A self-protecting system doesn't fall apart when a user goofs. Though not permissive, it must expect and tolerate user errors. We have already discussed how integrity relates to reliability. User privacy-by-default is a more precise description of isolation, and provides protection from accidental access.

[SLIDE: Security Requirements (2 of 2)]

Actually, access controls are a subset of resource controls. Resource controls also deal with the denial-of-service threat. Controlled sharing is where security is the name of the game, but need-to-know access controls are only one form of control. Access based on the identity of the user, and control based on ownership is another. Auditability is of course, more narrowly directed toward resource accountability. But it also provides a very effective user surveillance capability.

The one listed government security requirement without a commercial equivalent is the concept of security levels and categories. Actually, they are just different sets of criteria for the access controls mentioned above. The unique aspect is that levels and categories are independent of data ownership and subject to a mandatory policy. That's the hole we intend to fill.

With all of these similarities, it should not be surprising then, that a system meeting one set of requirements, should be easily adapted to the other. In fact, while adapting the NOS design to support levels and categories - we found that essentially all of the control mechanisms were already in place. The mechanisms only have to be extended to consider levels and categories and the mandatory security policy in the access control decision. It is clear that not only are the requirements similar, but are convergent on a common set of mechanisms. Simply put - form follows function. Thus we believe there is a common, generic set of control mechanisms which can be adapted to specific security policies. There's a bonus too - With those generic mechanisms already in place, we are confident that the Multilevel Security extensions will result in no significant performance degradation.

[SLIDE: NOS Multilevel Security]

With the NOS Multilevel Security extensions, we will have the <u>functional capability</u> to support Multilevel Mode operations. This will be a standard, fully equipped operating system, for use with our large scale, high performance computers. It will be compatible with the full line of CYBER 170 computers, and most predecessor machines. It will offer the full set of standard software products, and will be software compatible with existing NOS user applications. I )S with MLS will also be available not only to new customers, but to installed customers as well, which goes a long way toward the goal of "widespread availability."

That's what we are doing as practitioners of computer security. But how does that relate to the DoD Initiative and the theoretical work?

#### [SLIDE: Computer Security Approaches]

As you can see, Control Data has been approaching computer security from a practitioner's viewpoint. Our first concern has to be functional requirements, since we are selling not just hardware and software but capabilities. Design evolution recognizes the fact that we must maintain compatability with previous systems and the user's applications. Marketability is, in fact, not the least concern, but the one driving all other concerns.

From a theoretical approach, it is clear that computer security must begin with the design methodology, with the objective being provability. The idea of a formal evaluation and on-the-shelf certification is also important, and a pragmatic concern as well. But what really drives a manufacturer is marketability. In this case, it seems our concerns are markedly different. But let's look at the respective methodologies to see if that difference holds up on examination.

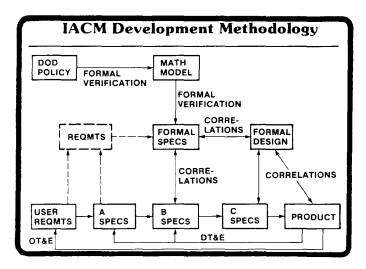

#### [SLIDE: Development Methodologies]

Here we can compare the formal design methodologies with those used by informal practitioners like Control Data. Obviously, both processes begin with some form of requirements. Formally, the security model serves as a target requirement. But as usual, a manufacturer is driven by market requirements, which are often conflicting and subject to internal constraints as well. Eventually, requirements are agreed upon and functional specifications are created. These are roughly equivalent to Top Level Specifications and here the two processes are very similar. In the formal process, the specs are then verified to the security model, while informally a Design Review occurs. A Design Review can be just as tough to do as a logical verification, and a lot more emotional. Where a detailed design is done formally, coding specs emerge informally. Now formal design correspondence may be <u>compute-intensive</u>, but peer review of all generated code is <u>people-</u> intensive. We're not sure which is more expensive, but neither is cheap! We have been told that complete code verification is beyond the

August 10, 1981

state-of-the-art, well complete system testing may be also - but we keep on trying. In penetration analysis we are doing essentially the same thing. At Control Data, we call it Malicious User Group or MUG system testing. Its <u>fun</u>, and occasionally very exciting! Finally, there is an evaluation of the resulting system by someone whose opinion is important to the developer. For commercial systems, it is simply market acceptance by the user. It would be nice however, to have a formal stamp of approval before shipping the system.

The objectives of these methodologies differ markedly however. For formal methodologies, it is <u>Provability</u>, but for commercial systems it is <u>Functionality</u>. In most other respects they are not only similar, but appear to Converge on a common set of developmental functions.

This convergence has encouraged Control Data to look into applying some of these formal methods to our system. As a first step in that direction, we have requested a DoD evaluation of our NOS system and Multilevel Security design. That process is underway, and so far it looks very promising. On the matter of formal design verification, we understand the benefits, but will have to develop the means of applying the theory to our practices. We are currently exploring some alternatives in that area.

[SLIDE: DoD Initiative Impact]

In conclusion, we at Control Data applaud the progress of the DoD Computer Security Initiative. We would especially like to congratulate you -

- o On increasing industry <u>awareness</u> of the need for security. (Some non-DoD people have helped too by getting caught.)

- o We thank you for fostering and occasionally funding the development of computer security technology.

- o Thanks too, for <u>focusing</u> computer security requirements for those not so knowlegeable in computer security. This directly benefits manufacturers by limiting the ingenuity of those who write technical specifications for procurements.

- o And finally, we thank you for providing an evaluation framework which places greater emphasis on <u>functional capabilities</u> than on technical specifications.

We look forward to a fruitful dialog on our common objectives of advancing the state-of-the-art, and acheiving the widespread availability of Trusted Computing Bases.

Thank you for the opportunity to address this forum.

[SLIDE: CDC Logo or DoD slide]

#### TOPICS

- CONTROL DATA AND SECURITY

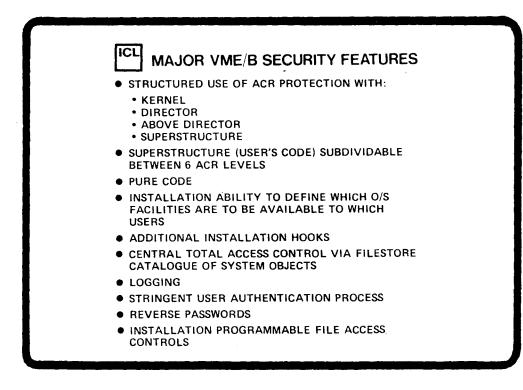

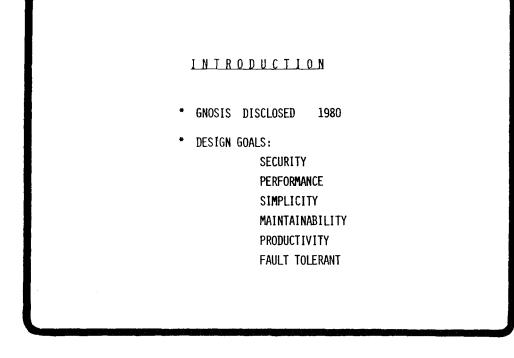

- SECURITY AND PERFORMANCE