# Arm<sup>®</sup> TrustZone<sup>®</sup> CryptoCell-712

**Revision 1.19**

# **FIPS 140-2 Non-Proprietary Security Policy**

Non-confidential

Copyright © 2016, 2017, 2018, Arm<sup>®</sup> Limited or its affiliates. All rights reserved.

# arm

#### **Copyrights and Trademarks**

Copyright © 2016, 2017, 2018, Arm<sup>®</sup> Limited or its affiliates. All rights reserved.

This document can be reproduced and distributed only whole and intact, including this copyright notice.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

# Contents

| Li | st of l | Figures       |                                                     | 1-6  |

|----|---------|---------------|-----------------------------------------------------|------|

| Li | st of ] | <b>Fables</b> |                                                     | 1-6  |

| 1  | Cry     | ptograp       | ohic Module Specification                           | 1-7  |

|    | 1.1     |               | le integration                                      | 1-7  |

|    | 1.2     |               | Cone <sup>®</sup> architecture, TEE and REE         |      |

|    | 1.3     | Appro         | ved security functions and mode of operation        | 1-9  |

|    |         | 1.3.1         | Approved security functions                         | 1-9  |

|    |         | 1.3.2         | Allowed security functions                          | 1-12 |

|    |         | 1.3.3         | Non-Approved security functions                     |      |

|    |         | 1.3.4         | Approved security mode                              | 1-13 |

|    | 1.4     | Comp          | onents and cryptographic boundary                   | 1-14 |

|    |         | 1.4.1         | Components                                          | 1-14 |

|    |         |               | 1.4.1.1 Shared Hardware                             |      |

|    |         |               | 1.4.1.1.1Symmetric Cryptography Engine              |      |

|    |         |               | 1.4.1.1.2Hardware Key Slots                         |      |

|    |         |               | 1.4.1.1.3 Inter-Core Connection                     |      |

|    |         |               | 1.4.1.2 TEE Hardware                                |      |

|    |         |               | 1.4.1.2.1 Asymmetric Cryptography Accelerator (PKA) |      |

|    |         |               | 1.4.1.2.2Non-Volatile Memory Manager                |      |

|    |         |               | 1.4.1.2.3 One-Time Programmable Memory (OTP)        |      |

|    |         |               | 1.4.1.2.4 True Random Number Generator (TRNG)       |      |

|    |         |               | 1.4.1.2.5 Persistent State Interface                |      |

|    |         |               | 1.4.1.2.6 Secure Timer                              |      |

|    |         |               | 1.4.1.2.7 Dedicated SRAM                            |      |

|    |         |               | 1.4.1.3 REE Hardware                                |      |

|    |         |               | 1.4.1.3.1 Dedicated SRAM                            |      |

|    |         |               | 1.4.1.4 TEE Firmware                                |      |

|    |         |               | 1.4.1.4.1 ROM Library                               |      |

|    |         |               | 1.4.1.4.2Cryptography Software (CRYS)               |      |

|    |         |               | 1.4.1.4.3Runtime Utility Functions                  |      |

|    |         |               | 1.4.1.4.4RAM Backup and Restore                     |      |

|    |         |               | 1.4.1.4.5 Deterministic Random Bit Generator (DRBG) |      |

|    |         |               | 1.4.1.4.6 Secure Boot                               |      |

|    |         |               | 1.4.1.4.7 Secure Debug                              |      |

|    |         |               | 1.4.1.4.8 Abstraction layers                        |      |

|    |         |               | 1.4.1.5 REE Firmware                                |      |

|    |         |               | 1.4.1.5.1 IV Generator                              |      |

|    |         | 1.4.2         | Cryptographic boundary                              | 2-21 |

| 2  | Port    |               |                                                     | 2-22 |

|    | 2.1     |               | nd REE Hardware Interfaces                          |      |

|    |         | 2.1.1         | APB Slave                                           |      |

|    |         | 2.1.2         | Interrupt                                           | 2-22 |

Copyright @ 2016, 2017, 2018,  $\mathrm{Arm}^{\circledast}$  Limited or its affiliates. All rights reserved.

|    | 2.2<br>2.3<br>2.4    | Shared Hardware Interfaces2-22.2.1AXI Master2-22.2.2Clocks2-22.2.3Power2-22.2.4Reset2-22.2.5Scan Interface2-22.2.5Scan Interface2-2REE Firmware2-22.4.1Linux Kernel Driver services2-22.4.2Status service3-2 | 22<br>23<br>23<br>23<br>23<br>23<br>23<br>23 |

|----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3  | Role                 | es, Services and Authentication 3-2:                                                                                                                                                                         | 5                                            |

| 5  | 3.1                  | Solution       3-2         Roles       3-2                                                                                                                                                                   |                                              |

|    | 3.2                  | Services                                                                                                                                                                                                     |                                              |

|    | 3.3                  | Authentication                                                                                                                                                                                               | 31                                           |

| 4  | Fin:4                | te State Model 4-3                                                                                                                                                                                           | <b>,</b>                                     |

| 4  | <b>F</b> IIII<br>4.1 | Deployed states                                                                                                                                                                                              |                                              |

|    | 4.2                  | Manufacturing and recovery states                                                                                                                                                                            |                                              |

| 5  | Phys                 | sical Security 6-3                                                                                                                                                                                           | 4                                            |

| 6  | One                  | rational Environment 7-3                                                                                                                                                                                     | 5                                            |

| U  | Oper                 | rational Environment 7-5.                                                                                                                                                                                    | 5                                            |

| 7  |                      | ptographic Key Management 7-3                                                                                                                                                                                |                                              |

|    | 7.1                  | User Keys                                                                                                                                                                                                    |                                              |

|    | 7.2                  | Platform Keys                                                                                                                                                                                                |                                              |

|    | 7.3                  | Key generation                                                                                                                                                                                               |                                              |

|    | 7.4                  | Key establishment                                                                                                                                                                                            |                                              |

|    | 7.5                  | Key entry and output                                                                                                                                                                                         |                                              |

|    | 7.6                  | Key storage                                                                                                                                                                                                  | 9                                            |

|    | 7.7                  | Key zeroization                                                                                                                                                                                              | 9                                            |

| 8  | Elect                | tromagnetic Interference / Compatibility (EMI/EMC) 9-4                                                                                                                                                       | D                                            |

| 9  | Self '               | Tests 9-4                                                                                                                                                                                                    | 1                                            |

|    | 9.1                  | Power-up tests                                                                                                                                                                                               | 1                                            |

|    |                      | 9.1.1 Cryptography test                                                                                                                                                                                      |                                              |

|    |                      | 9.1.1.1 Tests repeated in both TEE and REE                                                                                                                                                                   |                                              |

|    |                      | 9.1.1.2     Tests in REE     9-4       9.1.1.3     Tests in the TEE     9-4                                                                                                                                  |                                              |

|    |                      | 9.1.2 Firmware integrity test                                                                                                                                                                                |                                              |

|    | 9.2                  | Conditional tests                                                                                                                                                                                            |                                              |

| 10 |                      |                                                                                                                                                                                                              |                                              |

| 10 |                      | gn Assurance       11-4         Guidance                                                                                                                                                                     |                                              |

|    | 10.1                 | 10.1.1       Operator guidance                                                                                                                                                                               |                                              |

|    | 10.2                 | Proprietary documentation                                                                                                                                                                                    |                                              |

|    |                      |                                                                                                                                                                                                              |                                              |

Copyright © 2016, 2017, 2018, Arm® Limited or its affiliates. All rights reserved.

| 11 Mitigation of Other Attacks | 11-44 |

|--------------------------------|-------|

| Glossary                       | 45    |

| References                     | 46    |

# List of Figures

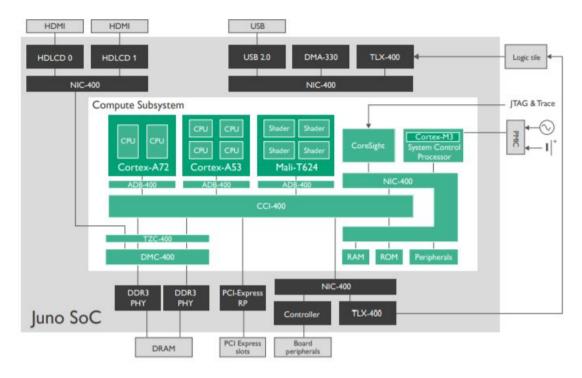

| 1 | Arm <sup>®</sup> Juno rev.2 board - hardware architecture |

|---|-----------------------------------------------------------|

| 2 | LogicTile FPGA board front                                |

| 3 | LogicTile FPGA board back 1-9                             |

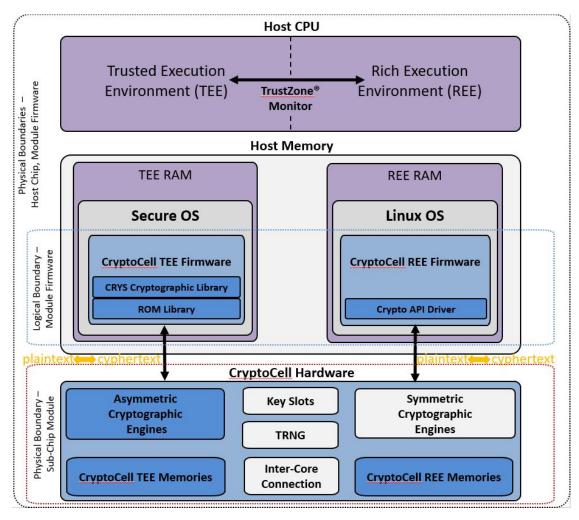

| 4 | CryptoCell-712 high level diagram                         |

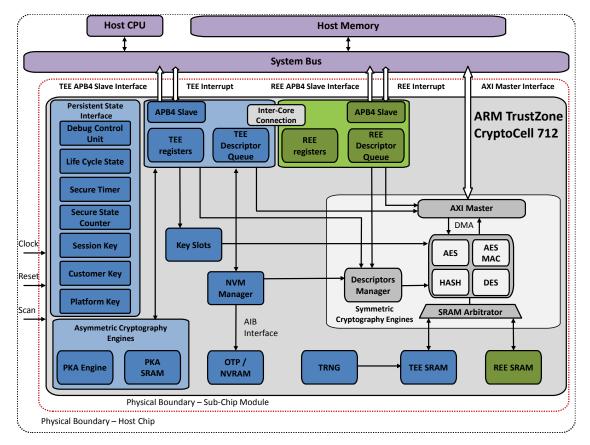

| 5 | CryptoCell-712 hardware diagram                           |

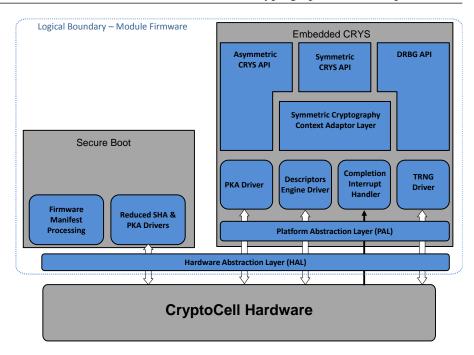

| 6 | TEE firmware components                                   |

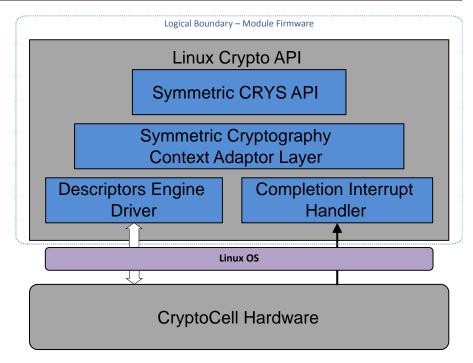

| 7 | REE firmware components                                   |

|   |                                                           |

# List of Tables

| 1 | Security levels                  |

|---|----------------------------------|

| 2 | Approved security functions      |

| 3 | Allowed security functions       |

| 4 | Non-Approved security functions  |

| 5 | Ports and interfaces             |

| 6 | Services                         |

| 7 | Module keys and CSPs             |

| 8 | User key sizes                   |

| 9 | Blocking access to platform keys |

# **1** Cryptographic Module Specification

This document is the non-proprietary security policy for Arm<sup>®</sup> TrustZone<sup>®</sup> CryptoCell-712. This security policy describes how CryptoCell-712 meets the security requirements of FIPS 140-2, and how to operate CryptoCell-712 securely, in a FIPS-compliant manner. This policy is submitted as part of the Federal Information Processing Standard (FIPS) 140-2 Level 1 validation process of CryptoCell-712. For more information about the Cryptographic Module Validation Program (CMVP), see: http://csrc.nist.gov/groups/STM/cmvp/.

CryptoCell-712 is a security engine with a root of trust and cryptographic accelerator capabilities. It is intended for use in an SOC (System on Chip), where it provides foundational security services for the entire platform, including cryptography, key management, platform identity, secure boot, secure Life Cycle State (LCS), and secure debug. It offers high-throughput cryptography engines suitable for a diverse set of use cases, such as secure playback of DRM (Digital Rights Management) protected media content, IPsec VPNs, TLS/SSL link protection, drive encryption and more.

Under the FIPS 140-2 definitions, the CryptoCell-712 is a firmware-hybrid module and a sub-chip module. The module includes hardware, defined in the RTL (Register Transfer Language), and firmware for execution on the host CPU, making it a hybrid module. The module's RTL is offered for integration as part of a silicon partner's (customer's) hardware host — an SOC, containing the cryptographic module's hardware alongside the Host CPU, memories and peripherals, making it a sub-chip component.

The following table depicts the security level claimed for each of the eleven sections that comprise the FIPS 140-2:

| FIPS | S 140-2 Sections                          | Security Level |

|------|-------------------------------------------|----------------|

| 1    | Cryptographic Module Specification        | 1              |

| 2    | Cryptographic Module Ports and Interfaces | 1              |

| 3    | Roles, Services and Authentication        | 1              |

| 4    | Finite State Model                        | 1              |

| 5    | Physical Security                         | 1              |

| 6    | Operational Environment                   | N/A            |

| 7    | Cryptographic Key Management              | 1              |

| 8    | EMI/EMC                                   | 1              |

| 9    | Self-Tests                                | 1              |

| 10   | Design Assurance                          | 1              |

| 11   | Mitigation of Other Attacks               | N/A            |

#### Table 1: Security levels

#### **1.1 Module integration**

CryptoCell-712 is primarily intended for integration as an IP (Intellectual Property) block into a partner's silicon product. The module is provided to partners as Silicon IP and accompanying firmware. The partner integrates the silicon with the host CPU hardware, and installs the firmware into the host NVRAM (Non Volatile Random Access Memory).

For the purposes of this Cryptographic Module Validation the module was tested on the expanded Arm<sup>®</sup> Juno rev.2 in a configuration reflecting partner's hosting SoC implementation. The expanded board contains compute subsystem running the operating firmware connected to the LogicTile FPGA (Field Programmable Gate Array) expansion with the synthesized hardware.

For ease of notation it shall be referred throughout the document as Arm<sup>®</sup> Juno board. Instead of the partner's applications, Arm<sup>®</sup> provides test software used to invoke the module's services. The FPGA board does not have some properties of a real silicon product, most importantly OTP (One-Time Programmable memory) which is only simulated (see Section 1.4.1.2.3).

Figure 1: Arm<sup>®</sup> Juno rev.2 board - hardware architecture

The implementation of the module is located on the LogicTile FPGA expansion as presented in Figure 1.

Figure 2: LogicTile FPGA board front

Figure 3: LogicTile FPGA board back

# 1.2 TrustZone<sup>®</sup> architecture, TEE and REE

CryptoCell-712 is intended for use in an Arm<sup>®</sup> TrustZone<sup>®</sup> platform, where a single Arm<sup>®</sup> Host processor runs two separate environments: a TEE (Trusted Execution Environment), and a REE (Rich Execution Environment). The TrustZone<sup>®</sup> architecture uses a single CPU to run both the TEE and the REE, with dedicated hardware enforcing the separation between control states, data and memories belonging to the different components.

The firmware in the TEE is generally compact and strictly controlled by the manufacturer, and is typically dedicated to providing security services to applications in REE. The firmware in the REE consists of an OS (Operating System) kernel, controlled by the manufacturer, and an application layer, typically modifiable by the user. The host OS for this certification is Linux OS kernel version 3.18. The module is compatible with multiple Linux variants including Android.

The version numbers for this certification are:

- Hardware 712

- TEE firmware 1.1.0.48

- TEE secure boot ROM 1.0.0.1145

- REE firmware 1.1.0.49

The CryptoCell-712 hardware has some dedicated TEE and REE components, providing functionality to the corresponding host environment, and some shared components, including the Symmetric Cryptography Engine. The shared engine alternates between TEE and REE states, with hardware enforcement of data and memory separation similar to that of the host CPU. Other shared components communicate between the TEE and REE. A high level diagram of the module is shown in Figure 4.

# 1.3 Approved security functions and mode of operation

### 1.3.1 Approved security functions

CryptoCell-712 supports FIPS-approved security functions, as specified in Table 2. The following notes and caveats apply:

Figure 4: CryptoCell-712 high level diagram

1-10

- Triple-DES: To comply with [SP800-67], the user must not exceed 2<sup>28</sup> encryptions with the same key.

- SHA-1: not approved for signature generation, only for legacy signature verifications. Approved for other uses.

- RSA: the key generation interface supports public exponents of size up to and including  $2^{16}+1$ . Of these, only  $2^{16}+1$  is compliant with FIPS 186-4. The operator is instructed not to use smaller public exponents in Approved mode.

- Key Agreement Diffie-Hellman (KAS FFC): The CAVP certificate covers all of SP800-56A except KDF, which was not tested.

- Key Agreement Diffie-Hellman and EC-DH (Elliptic Curve Diffie Hellman) functions are only approved when used as part of a [SP800-56A] key agreement protocol, otherwise only allowed.

- Key Agreement Diffie-Hellman and EC-DH: According to SP800-56A, externally received public keys and domain parameters must be validated. The operator is instructed to invoke the module's domain parameter and public key validation functions provided for this purpose.

- RSA and ECDSA: Only Approved hash functions must be used for signature generation. SHA-1 is only Approved for legacy signature verification.

| CAVP Cert                | Algorithm                                             | Standard                                        | Mode /<br>Method                                     | Key Lengths,<br>Curves or<br>Moduli | Use                                                                                                 | REE | TEE |

|--------------------------|-------------------------------------------------------|-------------------------------------------------|------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|

| REE: #4743<br>TEE: #4749 | AES                                                   | [FIPS-197,<br>SP800-38A,<br>SP800-38E]          | ECB, CBC, OFB,<br>CTR, XTS-AES                       | 128, 192, 256,<br>512 (XTS)         | Encryption /<br>decryption                                                                          | ~   | 1   |

| Vendor-<br>affirmed      | AES                                                   | [SP800-38Aadd]                                  | CBC-CS1                                              | 128, 192, 256                       | Encryption /<br>decryption                                                                          | 1   | 1   |

| REE: #4743<br>TEE: #4749 | AES                                                   | [SP800-38C]                                     | ССМ                                                  | 128, 192, 256                       | Authenticated<br>encryption /<br>decryption                                                         | 1   | 1   |

| REE: #4743<br>TEE: #4749 | AES                                                   | [SP800-38B]                                     | CMAC                                                 | 128, 192, 256                       | Message authentication                                                                              | 1   | 1   |

| REE: #2522<br>TEE: #2523 | Triple-DES                                            | [FIPS-46-3,<br>SP800-67]                        | ECB, CBC                                             | 192                                 | Encryption /<br>decryption                                                                          | 1   | 1   |

| REE: #3887<br>TEE: #3892 | SHS                                                   | [FIPS-180-4]                                    | SHA-1, SHA-224,<br>SHA-256, SHA-384,<br>SHA-512      |                                     | Message authentication                                                                              | ~   | ~   |

| REE: #3158<br>TEE: #3163 | НМАС                                                  | [FIPS-198-1,<br>RFC2104]                        | HMAC SHA-1,<br>SHA-224, SHA-256,<br>SHA-384, SHA-512 |                                     | Message authentication                                                                              | ~   | ~   |

| #4743                    | AES                                                   | [JEDEC, 6.3.4,<br>9.4] [FIPS-197,<br>SP800-38A] | CBC for ESSIV                                        | 128, 256                            | Encryption /<br>decryption                                                                          | 1   |     |

| #4743                    | AES                                                   | [JEDEC, 6.3.2,<br>9.2] [FIPS-197,<br>SP800-38A] | CBC for BitLocker                                    | 128, 256                            | Encryption /<br>decryption                                                                          | 1   |     |

| #2593                    | RSA                                                   | [FIPS-186-4]                                    | SHA functions<br>PSS, PKCS1-v1.5                     | 2048, 3072                          | Signature<br>Generation /<br>Verification /<br>Key Generation                                       |     | 1   |

| #2596                    | RSA (Firmware Certificate Verification)               | [FIPS-186-4]                                    | PSS; SHA-256                                         | 2048                                | Signature<br>Verification                                                                           |     | 1   |

| #1385                    | CVL (KAS FFC)                                         | [SP800-56A]                                     | FFC                                                  | (2048, 224),<br>(2048, 256)         | Shared Secret<br>Computation                                                                        |     | 1   |

| #1385                    | CVL (ECC CDH)                                         | [SP800-56A]                                     | ECC                                                  | P-224, P-256,<br>P-384, P-521       | ECC CDH<br>Primitive                                                                                |     | 1   |

| #1184                    | ECDSA (Elliptic Curve<br>Digital Signature<br>Scheme) | [FIPS-186-4]                                    | SHA functions                                        | P-224, P-256,<br>P-384, P-521       | Signature<br>Generation /<br>Verification /<br>Key Pair<br>Generation /<br>Public Key<br>Validation |     | 1   |

| #151                     | KBKDF (Key Based<br>Key Derivation<br>Function)       | [SP800-108]                                     | Counter mode                                         | CMAC AES-128,<br>256                | Key derivation                                                                                      |     | 1   |

| #1386                    | CVL (ANS 9.63)                                        | [SP800-135,<br>ANSI-X9.63]                      | Section 5.1, ANS X9.63-2001                          |                                     | Key derivation                                                                                      |     | 1   |

| #1630                    | DRBG (Deterministic<br>Random Bit Generator)          | [SP800-90A]                                     | CTR-DRBG                                             | 256                                 | Random Bit<br>Generation                                                                            |     | 1   |

| Vendor-<br>affirmed      | СКС                                                   | [SP800-133]                                     |                                                      |                                     | Input to<br>asymmetric<br>key generation                                                            |     | 1   |

# Table 2: Approved security functions

- ESSIV: AES-CBC algorithm with proprietary method for IV generation. The encryption key is different from the key used in the IV generation operation. Both keys are same size, either 128 or 256 bit.

- Bitlocker: AES-CBC algorithm with proprietary method for IV generation. The encryption key is different from the key used in the IV generation operation. Both keys are same size, either 128 or 256 bit.

#### 1.3.2 Allowed security functions

CryptoCell-712 TEE also supports several FIPS-allowed security functions, as specified in Table 3.

#### Table 3: Allowed security functions

| Algorithm                                                                    | Caveat                                                                                                                           | Use                                                                                        |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| True Random Number Generator<br>[NDRNG]                                      | There is no NIST-approved standard for NDRNG                                                                                     | DRBG seeding and reseeding                                                                 |

| RSAES-OAEP [PKCS1]<br>Moduli: 2048, 3072                                     | NIST allows RSA encryption for<br>key wrapping only, but does not<br>approve it<br>Key establishment strength 112 or<br>128 bits | Encryption/decryption                                                                      |

| RSAES-PKCS1-v1_5 [PKCS1]<br>Moduli: 2048, 3072                               | NIST allows RSA encryption for<br>key wrapping only, but does not<br>approve it<br>Key establishment strength 112 or<br>128 bits | Encryption/decryption                                                                      |

| Diffie-Hellman [SP800-56A]                                                   | Key establishment strength 112 bits                                                                                              | Key agreement                                                                              |

| EC Diffie-Hellman [SP800-56A]<br>Curves: p224k1, p256k1                      | Key establishment strength 112 or 128 bits                                                                                       | Key agreement                                                                              |

| ECDSA (Elliptic Curve Digital<br>Signature Scheme)<br>Curves: p224k1, p256k1 | NIST allows non-NIST<br>recommended curves of at least<br>112 bit security strength                                              | Signature Generation /<br>Verification /<br>Key Pair Generation /<br>Public Key Validation |

The following notes and caveats apply:

• NIST allows RSA encryption/decryption for key wrapping only. Key establishment strength 112 or 128 bits.

#### 1.3.3 Non-Approved security functions

CryptoCell-712 also supports non-FIPS-approved security functions and modes, as specified in Table 4. The following notes and caveats apply:

- IVGEN RNG: see Section 1.4.1.5.1.

- Triple-DES: Supports 2-key bundles, which is no longer approved as of 2016. Enforces distinct keys. Rejects DES weak keys.

- The ECIES relies on CAVP validated components, as it consists of a key agreement step conforming to [SP800-56A] followed by a key derivation step conforming to [PKCS1] or [ANSI-X9.63]. Nevertheless the scheme itself is not FIPS-approved.

| Algorithm                                                                                                                                                      | Use                                                      | REE | TEE |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|-----|

| AES non-approved modes — CBC-MAC [ISO/IEC-9797-1:2011]                                                                                                         | Message authentication                                   |     | 1   |

| AES non-approved modes — XCBC-MAC [RFC3566]                                                                                                                    | Message authentication                                   | 1   | 1   |

| AES GCM and GMAC [SP800-38D]                                                                                                                                   | Encryption/decryption<br>Message authentication          | 1   |     |

| DES ECB, CBC [FIPS-46-3]                                                                                                                                       | Encryption/decryption                                    | 1   | 1   |

| Triple-DES ECB, CDC with 2-key bundles [FIPS-46-3, SP800-67]                                                                                                   | Encryption/decryption                                    | 1   | 1   |

| MD5 [RFC1321]                                                                                                                                                  | Message authentication                                   | 1   | 1   |

| HMAC-MD5 [FIPS-198-1, RFC2104]                                                                                                                                 | Message authentication                                   | 1   | 1   |

| IVGEN RNG (Random Number Generator)                                                                                                                            | IV generation                                            | 1   |     |

| ECIES (Elliptic Curve Integrated Encryption Scheme) [IEEE1363]<br>Curves: p160k1, p160r1, p160r2, p192k1, p224k1, p256k1, P-192,<br>P-224, P-256, P-384, P-521 | Key agreement                                            |     | 1   |

| KDF1 and KDF2 Key Derivation Functions [ISO/IEC-18033-2]                                                                                                       | Key derivation                                           |     | 1   |

| ECC key generation with Non-Approved sizes [FIPS-186-4]<br>Curves: p160k1, p160r1, p160r2, p192k1, P-192                                                       | Key generation                                           |     | 1   |

| ECDSA with Non-Approved sizes [FIPS-186-4]<br>Curves: p160k1, p160r1, p160r2, p192k1, P-192                                                                    | Signature generation / verification                      |     | 1   |

| KAS EC-DH key agreement [SP800-56A]<br>Curves: p160k1, p160r1, p160r2, p192k1, P-192                                                                           | Key agreement                                            |     | 1   |

| KAS DH (Diffie-Hellman) with Non-Approved sizes [SP800-56A] 1024 bits                                                                                          | Key generation<br>Key agreement                          |     | 1   |

| RSA with Non-Approved sizes [FIPS-186-4]<br>1024, 4096 bits                                                                                                    | Key generation<br>Signature generation /<br>verification |     | 1   |

#### Table 4: Non-Approved security functions

# 1.3.4 Approved security mode

The cryptographic module supports a single Approved mode of operation. On power-on, the module performs power-on self-tests as described in Section 9. On failure, the module enters the Error state; on success, the user chooses the mode of operation (Approved or Non-Approved) by passing a boolean parameter to the firmware initialization routine. The FipsGetState API can be used to check the mode at runtime, and returns Approved, Non-Approved, or Error state; this API is implemented in both the TEE the REE.

In the Approved mode, all approved security functions listed in Section 1.3.1 are available. The non-approved security functions listed in Section 1.3.3 can be accessed but are disallowed by policy. There is no enforcement mechanism in place, therefore it is the user's responsibility not to use the non-approved functions and services. In order to call any non-approved security functions and services (listed as Non-Approved in the service table), the user is instructed to perform a cold power-on and initialize the module in Non-Approved mode. All Approved services remain available in Non-Approved mode, and calling any Approved service temporarily puts the module into Approved mode with the exception of RSA Key Generation and ECC Key Generation (these services omit conditional tests in Non-Approved mode). It is the user's responsibility to avoid sharing user keys between the modes.

The user can only switch between Approved and Non-Approved mode through a power-on reset. All CSPs (Critical Security Parameters) stored in the module's registers are cleared on power-on reset. In the Approved mode, conditional tests are performed as described in Section 9.

# 1.4 Components and cryptographic boundary

### 1.4.1 Components

Figure 5: CryptoCell-712 hardware diagram

As described in the introduction, CryptoCell-712 consists of hardware and firmware components, some divided between the TEE and REE, and some shared. Figure 5 illustrates the hardware diagram.

All CryptoCell-712 hardware services are accessed through a firmware layer, providing a high-level interface to its functionality. The TEE is accompanied by a library exposing its functionality through a high-level API to other TEE code, and the REE is accompanied by a driver exposing a high-level interface to the REE kernel and applications.

Each environment's hardware has dedicated components for communication with the corresponding Host environment — bus connectors, register files for control and state passing, descriptor queues for task queuing and high-level control flow, interrupt and completion handling logic.

The symmetric cryptographic engines are shared between the TEE and REE. Descriptor management and memory arbitration ensure the separation of state and data between TEE and REE.

The TEE has additional components not exposed to the REE.

• An asymmetric cryptography accelerator engine, also known as a PKA (Public Key Accelerator).

- A TRNG (True Random Number Generator).

- A non-volatile memory manager in charge of OTP storage and LCS (Life Cycle State) management.

- A DRBG implemented in firmware.

- Additional security functions.

This section documents the major functional system components; for port and interface components responsible for carrying state and data signals to and from the host system, see Section 2.

#### 1.4.1.1 Shared Hardware

- **1.4.1.1.1 Symmetric Cryptography Engine** The symmetric cryptography engine consists of the following components:

- Cryptographic cores (AES encryption, AES message authentication, DES, MD5 and SHA hash functions, HMAC).

- A descriptor queue manager. The descriptor queue manager is responsible for high-level control flow, and allows firmware running on the Host CPU to queue multiple operations for processing by the cryptographic engines. An arbitrator ensures the correct descriptor queue is used in the each context TEE and REE.

- Input and output DMA (Direct Memory Access) blocks. The DMA blocks allow input and output from host RAM (Random Access Memory) to dedicated TEE and REE SRAM (Static Random Access Memory) blocks.

The module provides hardware isolation for handling of platform keys. The AES cipher can directly load platform keys without exposing them to the SRAM or the Host CPU. The results of some operations on platform keys are limited to loading directly into designated hardware key registers, allowing secure key derivation.

When in the REE context, the symmetric cryptography engine can also use symmetric AES keys loaded into key slots (Section 1.4.1.1.2).

**1.4.1.1.2 Hardware Key Slots** Hardware key slots are dedicated hardware registers which let TEE securely create symmetric keys for REE to use. The module offers a TEE service to set the key slot values, and the REE can specify a key slot (by index) when invoking AES services. Those are the only ways to access key slots; neither environment can read key slots, and the TEE itself cannot use them for encryption.

The module defines 4 HW (Hardware) key slots for use by REE AES services. The slots be used as individual keys of size 128, 192, 256 bits or as double keys of 2\*128 or 2\*256 bits. In the latter case, two slots are used in each invocation. This functionality serves AES XTS, ESSIV and BitLocker modes.

**1.4.1.1.3 Inter-Core Connection** Since the module's TEE and REE components of the module have separate state and memories, CryptoCell-712 contains a dedicated mechanism for passing messages between the environments (here, referred to as cores). Consisting of a register and an interrupt signal, the mechanism allows each core to notify the other and pass basic information. This mechanism is used to synchronize the FIPS 140-2 state (Self-Test, Approved, Non-Approved, Error and error code if any) between TEE and REE.

#### 1.4.1.2 TEE Hardware

- **1.4.1.2.1** Asymmetric Cryptography Accelerator (PKA) The Asymmetric Cryptography Accelerator or PKA (Public Key Accelerator) block operates as a large integer arithmetic logic unit. It supports all mathematical and logical operations required for implementing public-key cryptosystems based on the discrete-logarithm problem, the integer factorization problem, and the prime-field elliptic-curve discrete logarithm problem.

- **1.4.1.2.2** Non-Volatile Memory Manager The Non-Volatile Memory (NVM) Manager uses an internal, point-to-point Intel AIB (Intel Asynchronous Interface Bus Specification) interface to access a bank of OTP memory. For the contents of OTP memory, see Section 1.4.1.2.3. The NVM Manager processes the compactly-stored data in the OTP memory, and provides a high-level interface for the rest of the module.

Several CSPs such as platform keys and their hash values are stored in the OTP memory (see Section 7.2). The NVM Manager controls all access to these CSPs, protecting against unauthorized reading and modification.

**1.4.1.2.3 One-Time Programmable Memory (OTP)** The module is meant to use OTP to provide some security features. When synthesized in a partner's system-on-chip, the module uses an on-chip OTP bank based on eFuse or similar technology, depending on the manufacturer.

The FPGA board used for this validation can only simulate the write-once properties of real silicon OTP. Instead, the FPGA's Flash-based file system uses access permissions, allowing only administrative users to overwrite the contents of the file system. This enables behaviors not possible in the real silicon module, such as returning the module to normal operation from a terminal state. This functionality is used for FIPS 140-2 testing.

OTP bits can be written but cannot be erased, which has useful security properties. The OTP stores a counter of zero-bits alongside fields intended to be written exactly once, so that any modification to the field or its zero-bit counter invalidates them. This protection method is used to store non-modifiable values, such as keys and key hashes. The OTP also stores modifiable but monotonically changing fields: firmware version counters and LCS bitmaps. Any changes to those are made non-reversible by the properties of the OTP.

The OTP is used by the TEE to store data and control inputs used for various platform security functions, including platform keys and their hash values (Section 7.2), LCS, and TRNG configuration. The OTP memory is initialized at manufacturing time, and from that point on is hardware-limited to exclusive access through the Non-Volatile Memory Manager (Section 1.4.1.2.2).

- **1.4.1.2.4 True Random Number Generator (TRNG)** The TEE contains a TRNG, which cannot be accessed directly as a service, but can only be used as a source of entropy for seeding the DRBG of Section 1.4.1.4.5. The TRNG collects noise directly from hardware circuits without Host interaction, by sampling the output of a fast free-running ring oscillator.

- **1.4.1.2.5 Persistent State Interface** The Persistent State Interface stores some of the TEE state in the always-on power domain, which survives a warm reset or module sleep (see Section 2.2.3) but not cold power-on. In the module submitted for validation, this is an internal component; however, a host platform can add logic to consume its signals as inputs for other components inside the host's boundary. The Persistent State Interface is shown in Figure 5.

The Persistent State Interface contains the following components:

- LCS (Life Cycle State), as defined in Section 4. Firmware components access the LCS through a dedicated firmware service.

- The DCU (Debug Control Unit) register, driven by the Secure Debug mechanism (Section 1.4.1.4.7). A host platform can use it to control its hardware debug capabilities.

- State Counter: a 32-bit counter, used by the RAM Backup and Restore service (Section 1.4.1.4.4).

- The Session Key K<sub>SESS</sub>, used by the RAM Backup and Restore service (Section 1.4.1.4.4).

- Secure Timer: see Section 1.4.1.2.6. Firmware components access the Secure Timer through a dedicated firmware service.

- **1.4.1.2.6 Secure Timer** The TEE offers a secure timer, accessible through a firmware service.

- **1.4.1.2.7 Dedicated SRAM** TEE has a block of dedicated SRAM (Static Random Access Memory). This is primarily used by the PKA, the symmetric cryptography engines, and the TRNG entropy collector.

The section of SRAM used by the PKA is cleared on completion of every operation. It is additionally cleared on boot, in the Deployed and RMA (Return Merchandising Authorization) Life Cycle States (see Section 4). This ensures that any Security Critical Parameters and intermediate values used in computations do not pass between different Life Cycle States and different roles.

#### 1.4.1.3 REE Hardware

- **1.4.1.3.1 Dedicated SRAM** REE has a block dedicated SRAM (Static Random Access Memory) for its descriptor queue and other needs. The descriptor queue size is configurable by partners for improved performance or reduced size.

- **1.4.1.4 TEE Firmware** Figure 6 depicts the firmware components associated with the TEE. These are divided between the Secure Boot ROM (Read-Only Memory) library, the CRYS (Cryptographic Software Library), various runtime utility components, and the Hardware and Platform abstraction layers. The different functional components are described in detail below.

- **1.4.1.4.1 ROM Library** The ROM library provides critical security functions used during the initialization stages of the module and the host platform, including Secure Boot and Secure Debug certificate verification functionality. For the purposes of this validation, the library is implemented in a read-only file system rather than an actual ROM, but partners can choose an unmodifiable ROM implementation to improve trust in the initialization process.

- **1.4.1.4.2 Cryptography Software (CRYS)** The major TEE firmware component is the CRYS (Cryptographic Software Library), which in this module is implemented in firmware but may have software implementations. It offers cryptography functions which drive the module's hardware cryptography engines, and perform additional operations in firmware where needed. The CRYS APIs provide access to the symmetric and asymmetric cryptography engines described above in the hardware section, and the DRBG (Section 1.4.1.4.5).

Figure 6: TEE firmware components

- **1.4.1.4.3 Runtime Utility Functions** The utility library provides high-level functions for key management, timestamp management, RPMB (Replay Protected Memory Block) and LCS Management. It also includes the RAM Backup and Restore service below.

- **1.4.1.4.4 RAM Backup and Restore** The RAM Backup and Restore service allows the operator to save and load external (host) RAM state securely, in order to save the state over periods of sleep. The service derives a key using KBKDF (Key Based Key Derivation Function) from the Session Key  $K_{SESS}$ , and uses AES-128 CCM authenticated encryption to encrypt and authenticate the RAM contents passed to it on entry to sleep, and validate and decrypt the contents on resumption. In addition, the service uses a persistent 32-bit State Counter, kept in a dedicated hardware register in the Persistent State Interface (Section 1.4.1.2.5), to prevent rollback. The counter is cleared on power-on reset and incremented on every invocation of the backup service. The counter is included in the AES CCM authenticated encryption operation, as part of the nonce input. The restore operation fails if the counter does not match.

- **1.4.1.4.5 Deterministic Random Bit Generator (DRBG)** The DRBG is a [SP800-90A] CTR\_DRBG. The module creates a DRBG instance on boot with AES-256 as the underlying cipher, and uses it for all internal random number generation. The user can create additional instances of the DRBG. A DRBG instance holds its values V and Key.

The DRBG instance is seeded with 384 bits from the TEE TRNG (see Section 1.4.1.2.4), including 256 for the seed buffer and 128 for the personalization string.

**1.4.1.4.6 Secure Boot** The CryptoCell-712 Secure Boot component provides integrity services for CryptoCell-712 firmware and optionally other Host firmware. Secure Boot is performed during the power-on boot process, and validates the various components of the firmware image based

on a firmware manifest and a set of certificates stored in NVRAM. Its chain of trust is rooted in a public key hash  $H_{BK}$ , stored in OTP during manufacturing. Certificate and image verification uses PKCS#1v2.1 RSA-PSS-2048 with SHA-256 hashes.

Secure Boot supports the following features:

- Chaining of secondary certificates, to permit parts of the system image to be signed by other trusted developers

- Software confidentiality optional firmware decryption using AES-128 CTR with the Code Encryption Key (K<sub>CE</sub>)

- Support for firmware updates: an external mechanism can update the firmware image, manifest and certificates

- Image version revocation

Arm<sup>®</sup> provides tools for system and software providers to support certificate management, device provisioning, and the firmware image signing.

A security failure during Secure Boot, such as an invalid certificate, version mismatch, or signature mismatch, will cause boot failure and the module will enter the Error state.

**1.4.1.4.7 Secure Debug** The CryptoCell-712 Secure Debug mechanism is a security service provided by the module to the Host. The mechanism performs a boot-time security check on a debug certificate located in the NVRAM, and writes to the module's DCU (Debug Control Unit) register. On the FPGA submitted for this validation, the DCU has no further effect. Actual CryptoCell partners typically use the DCU to control the host's debugging capabilities, which provide authorized parties with extended access to the host CPU and RAM contents.

Secure Debug does not constitute a FIPS Maintenance mode, as it does not provide any extended access to the module itself. Secure Debug is also not managed as a Life Cycle State, since it is reversible. Since Secure Debug is associated with the manufacturer, it is assigned to the Crypto Officer.

In addition to validating a multi-tiered certificate chain on entry, the module takes additional steps to prevent access to Platform Keys during the Debug mode, preventing the leakage or misuse of any CSPs stored within, even by the original manufacturer.

Secure Debug certificates are device-specific. The certificate must contain a 256-bit SOC ID field, authenticated with the issuer's signature, which the module validates. The SOC ID must match the one produced by the module's Identify SOC service.

The Secure Debug certificate checking mechanism is also used to enter the RMA LCS. The certificates for RMA and for Secure Debug are identical, except for a flag indicating which mode the certificate allows to enter.

**1.4.1.4.8 Abstraction layers** The CryptoCell-712 defines several internal APIs in the HAL (Host Adaptation Layer) and PAL (Platform Adaptation Layer) firmware components in the TEE runtime library.

The HAL provides a firmware abstraction for the module's basic hardware capabilities, including interrupt and cache control, initialization and termination.

The PAL (Platform Adaptation Layer) provides a firmware abstraction to the module's interface with the Host OS, and includes functions for initialization and termination, DMA control, memory allocation, memory mapping and basic memory manipulation functions such as memcopy, and synchronization primitives such as mutexes and barriers. The implementation provided by Arm<sup>®</sup> is functional and adapted to the reference implementation submitted for

Figure 7: REE firmware components

validation. The partner is expected to replace some HAL (Host Adaptation Layer) and most PAL function implementations, as needed to adapt them to the Host OS of their choice. The partner should refer to the module's Integration Guides for details on adapting those layers.

**1.4.1.5 REE Firmware** Figure 7 depicts the firmware components associated with the REE. The firmware exposes the CRYS functionality in a high-level form, accessible to the host OS.

The firmware is a standard Linux Kernel driver, which registers with the OS as a platform device driver. The driver registers the services it provides as Linux kernel crypto algorithms, as detailed in Section 2.4.1.

The driver interfaces allow the OS kernel and application code to invoke the REE crypto functionality, while using caller-supplied keys or key slots (Section 1.4.1.1.2).

1.4.1.5.1 IV Generator Linux cryptographic interfaces support an optional invocation mode in which the IV (Initialization Vector) is generated internally, rather than passed in as a parameter by the caller. For this purpose, the REE firmware contains a non-approved RNG called IVGEN. IVGEN is seeded from the Linux kernel API get\_random\_bytes(), invokes the module's AES CTR service to expand the seed into a 1KB buffer, and uses that buffer to return IVs on request. Once the buffer runs out, it is regenerated. This design allows for efficient IV generation in performance-intensive scenarios.

IVGEN is not offered as a random number generation service by the module; it is only available for IV generation in REE algorithms. This RNG is non-approved because it does not implement the CRNGT (Continuous Random Number Generator Test). The operator is instructed not to use IVGEN in the FIPS-Approved Mode.

#### 1.4.2 Cryptographic boundary

The module's hardware is integrated into the Host silicon, the module's firmware is stored in the host's NVRAM, and the module firmware is executed on the Host CPU (see Section 1.1). All the module components are contained in the Host SOC package. Since the module firmware runs on the general-purpose Host CPU, the module is defined as a sub-chip firmware-hybrid module, and has four cryptographic boundaries, as defined below and shown in Figure 4.

The sub-chip subsystem boundary is defined as the set of circuitry specified by the module's RTL and terminating at the module's hardware interfaces, listed in Section 2, along with the module's firmware components specified by the module's binaries. The sub-chip hardware physical boundary is defined as the single-chip physical boundary, corresponding to the Host SOC in which the module is integrated.

The physical boundary of the firmware is the platform on which the firmware and OS reside, in this case the Host SOC which includes the memories where the firmware is stored and the CPU on which it is executed. The logical boundary of the firmware is the set of firmware components that implement the module's cryptographic and related functionality, and is wholly contained within the physical boundary.

# 2 Ports and Interfaces

The module supports a number of physical and logical ports and interfaces, as shown in Table 5 and described in detail below. The AXI and APB buses and interrupt signals are used exclusively by the module's firmware, and carry data, control and status between the module's firmware and hardware.

| Туре                                               | Interfaces                          | TEE          | REE          |

|----------------------------------------------------|-------------------------------------|--------------|--------------|

| Power Input                                        | Power                               | $\checkmark$ | $\checkmark$ |

|                                                    | Clock                               | $\checkmark$ | $\checkmark$ |

| Control Innut                                      | Reset                               | $\checkmark$ | 1            |

| Control Input                                      | Scan                                | $\checkmark$ | $\checkmark$ |

|                                                    | APB (AMBA Peripheral Bus)           | 1            | 1            |

| APB (AMBA Peripheral Bus)       Firmware API calls |                                     | ✓            | $\checkmark$ |

| Status Output                                      | Interrupt                           | $\checkmark$ | ✓            |

| Status Output                                      | Firmware API return values          | $\checkmark$ | $\checkmark$ |

| Data Input                                         | AXI (Advanced eXtensible Interface) | $\checkmark$ | 1            |

| Data Input                                         | Firmware API input arguments        | $\checkmark$ | $\checkmark$ |

| Data Output                                        | AXI                                 | $\checkmark$ | $\checkmark$ |

| Data Output                                        | Firmware API output arguments       | $\checkmark$ | $\checkmark$ |

### Table 5: Ports and interfaces

# 2.1 TEE and REE Hardware Interfaces

The following interfaces are duplicated, and present in both TEE and REE.

#### 2.1.1 APB Slave

The two APB (AMBA Peripheral Bus) slaves are used to control the TEE and REE operation. The Host accesses each APB slave as a memory-mapped input/output device. The interface provides access to the module's control registers, and serves to pass descriptors and trigger hardware operations.

# 2.1.2 Interrupt

Both REE and TEE have an interrupt signal to attract a Host's attention on operation completion or error. Information on the cause of the interrupt is available through dedicated memory-mapped registers.

# 2.2 Shared Hardware Interfaces

#### 2.2.1 AXI Master

The AXI (Advanced eXtensible Interface) Master is used to pass data between the host memories and the symmetric cryptographic engine's memories. It implements the AXI protocol with

The module has multiple internal clock domains, with a separate clock domain for each cryptographic engine. All internal clocks are derived from a single clock signal supplied from the host system.

# 2.2.3 Power

The REE and TEE receive power from the host. When not in use (e.g. during host sleep), the host may power down the REE and TEE hardware, and later turn the hardware back on when needed. The module keeps internal state that needs to be preserved during warm power down in the always-on Persistent State Interface (Section 1.4.1.2.5). The module's firmware, running on the Host CPU, contains logic for orderly suspension and resumption of module operations on power down.

# 2.2.4 Reset

The module supports a reset signal, which clears all hardware state and registers. This does not affect the module's firmware state.

# 2.2.5 Scan Interface

The module supports a scan input signal. This signal drives the module's reset line, clearing keys stored in hardware registers. In the TEE, asserting the scan line has the additional effect of making platform keys inaccessible (see Section 7.2.1).

Partners commonly implement scan logic capabilities, allowing to test and extract the contents of memories and registers during manufacturing. The module submitted for the purposes of this validation does not contain such scan logic, however the scan interface security features are present.

# 2.3 TEE Firmware

The TEE firmware exposes its services through library APIs functions. See Table 6 for the full list of services. Documentation for the API functions implementing those services is available in the full proprietary documentation package.

# 2.4 REE Firmware

# 2.4.1 Linux Kernel Driver services

The REE Firmware is a standard Linux Kernel platform device driver. The driver registers itself as a Linux kernel cryptographic algorithms provider, and offers cryptographic services to applications and kernel components. The module's services are registered under a set of string identifiers, which are listed in the full proprietary documentation package.

The REE AES algorithms can use key slots keys, specifying them by index, as well as user keys.

#### 2.4.2 Status service

Other than the Linux driver services, the REE firmware offers one service API:

• FipsGetState: FIPS Status API, returns the mode (Approved, Non-Approved, Error) and error code if any.

# 3 Roles, Services and Authentication

### 3.1 Roles

CryptoCell-712 offers high-level cryptographic services which operate on CSPs and user inputs, as well as platform security services which can be used by the Host platform to establish a root of trust. In addition, the module defines separate states for manufacturing and manufacturer-authorized recovery and debug.

The following two roles are defined:

#### **User Role**

The user is defined as the set of firmware applications running in the TEE and REE, when the module is in Deployed state. This role accesses cryptographic services, including Approved and non-Approved security functions, as well as platform security services.

#### Crypto Officer Role

The Crypto Officer is defined as the platform's manufacturer. The Crypto Officer is responsible for initializing the module's NVRAM and OTP, in order to make the module operational. This role has exclusive access to the services that change the module's Life Cycle State. States designated for the Crypto Officer are Chip Manufacturing, Device Manufacturing, RMA, and Security Disabled. The Secure Debug service (see Section 4) is designated to the Crypto Officer.

The module does not define a Maintenance Role. While the module does enable the operator to enter the Secure Debug and RMA modes after the module has already been in the Deployed state, those states do not provide additional access to CSPs in the module. Secure Debug and RMA are assigned to the Crypto Officer Role, and limited to holders of certificates signed by the manufacturer.

# 3.2 Services

Table 6 below lists the services offered by CryptoCell-712, along with a concise description of purpose, the list of security functions offered or used by the service, a list of keys in use and the access types for each, the role that can access that service, the Approved or Non-Approved status, whether it's supported in TEE or REE, and the operator's access rights to any keys and CSPs involved.

Note that when a service is implemented by both REE and TEE, the same hardware is being used, with different firmware components passing the arguments and triggering the operations.

Access to keys is denoted with a single letter:

- I input keys from the user,

- O output keys to the user,

- R read keys from internal storage,

- W write keys to internal storage,

- Z zeroize.

Access type is defined by the perspective of the module or the service. Input and read access also includes any internal usage for the read key.

#### **Table 6: Services**

| Service Name                       | Purpose                          | Security Functions                                                                           | Keys cy<br>and D<br>CSPs                                                                | User Role | CO Role | Approved | REE | TEE |

|------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------|---------|----------|-----|-----|

| AES — TEE<br>Approved              | Encryption<br>Decryption         | AES-128, 192, 256<br>ECB, CBC, CTR,<br>OFB, CMAC, XTS,<br>CTS (CBC-CS1)                      | Input:User keys- I $K_{CST}$ - R $K_{DR}$ - R $K_{SESS}$ - R $K_{PLT}$ - R <sup>1</sup> | 1         |         | 1        |     | 5   |

| AES — TEE<br>Non-Approved modes    | Encryption<br>Decryption         | AES-128, 192, 256<br>XCBC-MAC                                                                | Input:User keys- I $K_{CST}$ - R $K_{DR}$ - R $K_{SESS}$ - R $K_{PLT}$ - R              | 1         |         |          |     | 1   |

| AES — REE<br>Approved              | Encryption<br>Decryption         | AES-128, 192, 256<br>ECB, CBC, CTR,<br>OFB, CMAC, XTS,<br>CTS (CBC-CS1),<br>ESSIV, BitLocker | Input:<br>User keys - I<br>Key slots - R                                                | -         |         | 1        | ~   |     |

| AES — REE<br>Non-Approved modes    | Message<br>authentication        | AES-128, 192, 256<br>modes: XCBC-MAC,<br>GCM, GMAC                                           | Input:<br>User keys - I<br>Key slots - R                                                |           |         |          | 1   |     |

| Triple-DES<br>Approved             | Encryption<br>Decryption         | Triple-DES ECB, CBC<br>with three-key bundles<br>(DED and EDE)                               | Input:<br>User keys - I                                                                 | 1         |         | 1        | 1   | 1   |

| Two-Key Triple-DES<br>Non-Approved | Encryption<br>Decryption         | Triple-DES ECB, CBC<br>with two-key bundles<br>(DED and EDE)                                 | Input:<br>User keys - I                                                                 | 1         |         |          |     | 1   |

| DES<br>Non-Approved                | Encryption<br>Decryption         | DES ECB, CBC                                                                                 | Input:<br>User keys - I                                                                 | 1         |         |          |     | 1   |

| SHA<br>Approved                    | Message<br>authentication        | SHA-1 <sup>2</sup> , SHA-224,<br>SHA-256, SHA-384,<br>SHA-512                                |                                                                                         | 1         |         | 1        | 1   | 1   |

| MD5<br>Non-Approved                | Legacy message<br>authentication | MD5                                                                                          |                                                                                         | 1         |         |          | 1   | 1   |

| HMAC Approved<br>functions         | Message<br>authentication        | HMACSHA-1,SHA-224,SHA-256,SHA-384,SHA-512                                                    | Input:<br>User keys - I                                                                 | ~         |         | 1        | 1   | 1   |

| HMAC-MD5<br>Non-Approved           | Legacy message authentication    | HMAC-MD5                                                                                     | Input:<br>User keys - I                                                                 | 1         |         |          | 1   | 1   |

$<sup>{}^{1}</sup>K_{DR}$  is limited by firmware to use in key derivation only.  $K_{SESS}$  and  $K_{PLT}$  are internally used by the module for encryption/decryption, and the operator is instructed to use those keys only for encryption or decryption, to conform to [SP800-57] Section 5.2 "Key Usage".

<sup>&</sup>lt;sup>2</sup>SHA-1 is not approved for signature generation, Approved for legacy signature verification and other uses.

|                                                                                     | 1                                                                           | л                                                                                                        |                                                                                                                |                       |           |         |          |     |     |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------|-----------|---------|----------|-----|-----|

| Service Name                                                                        | Purpose                                                                     | Security Functions                                                                                       | Keys<br>and<br>CSPs                                                                                            | Key Anness            | User Role | CO Role | Approved | REE | TEE |

| NIST SP800-108 Key<br>Derivation Function<br>Approved                               | KBKDF (Key Based<br>Key Derivation<br>Function) [SP800-108]                 | KDF in Counter Mode.<br>AES-128 or AES-256<br>in CMAC mode                                               | Input:User keys- $K_{DR}$ - $K_{PLT}$ - $K_{OEM}$ -Output:-User keys- $K_{SESS}$ - $K_{PLT}$ - $K_{OEM}$ - $C$ | R<br>R<br>I<br>J<br>7 | \$        |         | 1        |     | ~   |

| NIST SP800-135 Key<br>Derivation Functions<br>Approved                              | Key derivation [SP800-135] <sup>3</sup> .                                   | SHA-1,       SHA-224,         SHA-256,       SHA-384,         SHA-512       SHA-384,                     | Input:<br>User keys<br>Output:<br>User keys - C                                                                |                       | <         |         | 1        |     | 1   |

| KDF1 and KDF2 Key<br>Derivation Functions<br>Non-Approved                           | Key derivation<br>functions KDF1<br>and KDF2<br>[ISO/IEC-18033-2]           | SHA-1,       SHA-224,         SHA-256,       SHA-384,         SHA-512       SHA-384,                     | Input:<br>User keys - 2<br>Output:<br>User keys - C                                                            |                       | ~         |         |          |     | 1   |

| Endorsement Key<br>Derivation                                                       | Derive the<br>Endorsement Key<br>ECC key-pair                               | ECC key pair generation <sup>4</sup>                                                                     | Input: $K_{DR}$ - FOutput:PubK_S- CPrivK_S- C                                                                  | )                     | ~         |         | 1        |     | 1   |

| RPMB (Replay<br>Protected Memory<br>Block) Key Derivation                           | Derive K <sub>RPMB</sub> from<br>K <sub>DR</sub> using KBKDF<br>[SP800-108] | KBKDF                                                                                                    | Input:         K <sub>DR</sub> - F         Output:       - C         K <sub>RPMB</sub> - C                     |                       | ~         |         | 1        |     | 1   |

| RPMB Page MAC<br>Generation                                                         | RPMBFrameauthentication[JESD84]                                             | HMAC SHA-256                                                                                             | Input:<br>K <sub>RPMB</sub> -                                                                                  | I                     | ~         |         | 1        |     | 1   |

| ECC (Elliptic Curve<br>Cryptography) Key<br>Generation<br>Approved                  | ECC key generation<br>[FIPS-186-4]                                          | Curves:<br>P-224, P-256, P-384,<br>P-521, p224k1,<br>p256k1. <sup>5</sup><br>Uses DRBG.                  | Output:<br>User keys - C<br>Sizes:<br>224, 256, 384, 521 bits                                                  |                       | 1         |         | 1        |     | 1   |

| ECC (Elliptic Curve<br>Cryptography) Key<br>Generation<br>Non-Approved<br>strengths | ECC key generation<br>[FIPS-186-4]                                          | Curves:<br>P-192, p160k1, p160r1,<br>p160r2, p192k1, <sup>6</sup><br>user-defined domains.<br>Uses DRBG. | Output:         User keys       - C         Sizes:       160, 192 bits                                         | )                     | ~         |         |          |     | 1   |

| ECC Public Key<br>Validation                                                        | Public key validation                                                       |                                                                                                          | Input:<br>User keys -                                                                                          | I                     | ~         |         | 1        |     | 1   |

<sup>&</sup>lt;sup>3</sup>This includes key derivation methods ASN1DER and Concatenation specified in [ANSI-X9.42, 7.7.1] and [ANSI-X9.63, 5.6.3], approved when used as part of a [SP800-56A] agreement scheme

<sup>&</sup>lt;sup>4</sup>The private key is derived according to [FIPS-186-4, Section B.4.1], but instead of a random input from a RBG (Random Bit Generator), the procedure uses the result of a [SP800-108] KBKDF applied to the  $K_{DR}$ . The resulting key pair has a different value per module, permanent until zeroization.

<sup>&</sup>lt;sup>5</sup>Security strengths for non-NIST-recommended curves: p224k1 — 112 bits, p256k1 — 128 bits.

<sup>&</sup>lt;sup>6</sup>Security strengths for non-NIST-recommended curves: p160k1, p160r1, p160r2 — 80 bits, p192k1 — 96 bits.

|                                                                           |                                                                            |                                                                                             |                                                                                                                                                                      |           |         | 1        |     |     |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|----------|-----|-----|