# FIPS140-2 Non Proprietary Security Policy

# ECI TR10\_4EN Encryption Module

Hardware Part No: Board-Type=0x856B, Revision# D3

Firmware Revision: R6.3

System Name Sub System Name Module Name Author Apollo IO TR10\_4E

TR10\_4EN Milind Barve

Revision 1.6

Release Date 18-Apr-2016

Document ID <u>2EVYDPYSQPWJ-112-1807</u>

© ECI Telecom Ltd. http://www.ecitele.com

# Contents

| FII | PS140-  | 2 No        | n Proprietary Security Policy          | 1  |

|-----|---------|-------------|----------------------------------------|----|

| Re  | eferenc | es          |                                        | 3  |

| 1   | Intr    | oduc        | tion                                   | 3  |

|     | 1.1     | Doc         | ument Organization                     | 4  |

| 2   | Мо      | dule (      | Overview                               | 5  |

|     | 2.1     | Syst        | em Level Block Diagram                 | 5  |

|     | 2.2     | Mo          | dule Specification                     | 6  |

|     | 2.2.    | 1           | Main Firmware Components On Board      | 7  |

|     | 2.3     | Mo          | dule Ports & Interfaces                | 7  |

|     | 2.3.    | 1           | Data Ports                             | 7  |

|     | 2.3.    | 2           | Debug Port                             | 7  |

|     | 2.3.    | 3           | Management Ethernet                    | 7  |

|     | 2.3.    | 4           | Summary of FIPS140-2 Interfaces        | 8  |

|     | 2.3.    | 5           | Physical versus Logical IO mappings    | 9  |

|     | 2.3.    | 6           | Roles of LEDS                          | 9  |

|     | 2.4     | Role        | es & Services                          | 10 |

|     | 2.4.    | 1           | Roles                                  | 10 |

|     | 2.4.    | 2           | Services                               | 11 |

|     | 2.5     | Aut         | hentication Mechanism                  | 12 |

|     | 2.6     | Fini        | te State Model                         | 12 |

|     | 2.7     | Phy         | sical Security                         | 12 |

|     | 2.8     | Env         | ironmental Failure Testing/ Protection | 13 |

|     | 2.9     | Оре         | rational Environment                   | 13 |

|     | 2.10    | Cry         | otographic Key Management              | 14 |

|     | 2.10    | ).1         | Approved Cryptographic Algorithms      | 15 |

|     | 2.10    | ).2         | Lifecycle of Keys                      | 15 |

|     | 2.10    | ).3         | Key Zeroization                        | 16 |

|     | 2.10    | ).4         | Protection of Keys                     | 17 |

|     | 2.10    | ).5         | Storage of Keys                        | 17 |

|     | 2.11    | Self        | -Tests                                 | 17 |

|     | 2.11    | L. <b>1</b> | Power-up Self Tests                    | 18 |

|     | 2.11    | L.2         | Conditional Self Tests                 | 19 |

|     | 2.11    | .3          | Summary of Self Tests                  | 19 |

|   | 2.12   | Design Assurance              | . 19 |

|---|--------|-------------------------------|------|

|   | 2.13   | Mitigation of Attacks         | . 20 |

| 3 | Secu   | ure Operation                 | . 20 |

|   | 3.1    | Module Installation           | . 20 |

|   | 3.2    | Initial Key Loading           | . 21 |

|   | 3.3    | Administrator Guidance        | . 21 |

|   | 3.4    | Security Officer              | . 22 |

|   | 3.5    | Documentation Note            | . 22 |

|   | 3.6    | Traceability & Identification | . 22 |

|   | 3.6.   | 1 Hardware Identification     | . 22 |

|   | 3.6.   | 2 Firmware Traceability       | . 23 |

|   | Acrony | yms                           | . 24 |

# References

| ID | Title                     | Author            | Revision | File Location      |

|----|---------------------------|-------------------|----------|--------------------|

| 1  | FIPS-140-2                | US Dept. of       | 2001-05- | FIPS-140-2         |

|    |                           | commerce          | 25       |                    |

| 2  | FIPS-197 (AES)            | US Dept. of       |          | FIPS-197 URL       |

|    |                           | commerce          |          |                    |

| 3  | FIPS standard archive     | US Dept. of       |          | FIPS-Archive-URL   |

|    |                           | commerce          |          |                    |

| 4  | FIPS Annex-A (approved    | US Dept. of       |          | FIPS-140-2 Annex-A |

|    | security functions)       | commerce          |          |                    |

| 5  | FIPS 140-2 Implementation | US Dept. of       |          | FIPS-150-2 IG      |

|    | Guidance                  | commerce          |          |                    |

| 6  | Recommendation for Block  | NIST, US Dept. of |          | <u>SP800-38D</u>   |

|    | Cipher Modes of Operation | commerce          |          |                    |

# 1 Introduction

This document covers the non-proprietary security policy for ECI's TR10\_4EN module. This document is prepared in the context of FIPS140-2 standard compliance of the module. TR10\_4EN is a transponder module with line side encryption in ECI's Apollo product line.

FIPS140-2 is part of the <u>FIPS</u> (Federal Information Processing Standards) publications of the United States Federal Government. FIPS is targeted at applications dealing with non-classified but sensitive information. It serves as an important reference even across various non US security establishments

worldwide. Consequently vendors of information processing / communication equipment target FIPS compliance.

<u>CMVP</u> (Cryptographic Module Validation Program) validates cryptographic modules to FIPS140-2 and other cryptography based standards. CMVP is a joint effort between US (NIST) and Canadian (CSE) federal governments. TR10\_4EN complies with CMVP requirements. CMVP compliance is a mandatory acceptance criterion for equipment vendors dealing with US & Canadian federal agencies.

ECI is marketing this card with its current firmware release (R6.3) that meets FIPS140-2 Level-1 compliance overall. The following table explicitly covers FIPS compliance level for each of the sections in this document.

| Section Name                            | FIPS Compliance Level |

|-----------------------------------------|-----------------------|

| Cryptographic Module Specification      | 1                     |

| Cryptographic Module Ports & Interfaces | 1                     |

| Roles, Services & Authentication        | 1                     |

| Authentication                          | 1                     |

| Finite State Model                      | 1                     |

| Physical Security                       | 1                     |

| Operational Environment                 | N/A                   |

| Cryptographic Key Management            | 1                     |

| Self-Tests                              | 1                     |

| Design Assurance                        | 1                     |

| Mitigation of Attacks                   | N/A                   |

**Table 1: Summary of FIPS Compliance Levels**

# 1.1 Document Organization

The following document is organized into two main sections. The first one covers structural/ architectural aspects of TR10\_4EN (hereby referred as 'the module' or 'the card') while the subsequent section covers security aspects during the operational mode.

ECI is submitting the following documents in addition to the current (**S**ecurity **P**olicy) as a part of FIPS certification:

- 1. Finite State Model

- 2. Vendor Evidence

- 3. Product Documentation

- 4. CAVP Certifications received for approved cryptographic algorithms in the module.

Extensive pointers to various relevant standards and literature references have been provided through the <u>reference</u> & <u>acronym</u> tables.

### 2 Module Overview

# 2.1 System Level Block Diagram

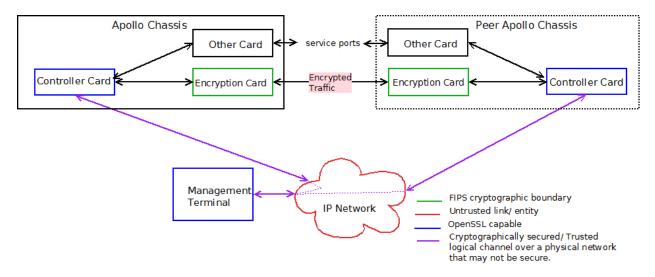

The following block diagram provides a system level overview of TR10\_4EN transponder application. It covers the control plane as well as data-plane aspects of the card. We shall use the term 'IO card' or 'IO' to refer to TR10 4EN card in the rest of this document.

Fig 1: System Level Overview

As shown in the diagram above, the encryption card exchanges traffic in an encrypted form with remote peers. Each card has 2 line side ports; therefore it can have up to 2 remote peers. Keys for encrypting/decrypting the traffic are established through control plane signaling.

Each line is bidirectional and there are different encryption keys active in each direction at any given time. Controller cards in each chassis are responsible for establishing these keys in a secure manner. The controller card downloads each active key to relevant IO cards in a FIPS compliant manner.

<u>FIPS Cryptographic boundary</u>: FIPS compliant cryptographic modules in the above diagram are marked as 'Encryption Card' with green outlines. The green outline is the cryptographic boundary for FIPS purposes.

# 2.2 Module Specification

TR10\_4EN is a '1U' sized card that fits into ECI's Apollo chassis. ECI is seeking FIPS certification only for this module in its upcoming release (R6.3). Other card types or the Apollo chassis are not part of this FIPS certification. The module is shown in the following pictures:

Fig. 2: TR10\_4EN Physical Module (Top View)

Fig 3: TR10 4EN Physical Module (Bottom View)

The module shown in the above pictures is a 'multi-chip embedded cryptographic module' as per the FIPS terminology (FIPS140-2 section 4.5.3). It draws its power from Apollo backplane and also receives commands/ control information & parameters through its backplane Ethernet interface.

Physically the module comprises of a base board and 2 mezzanine boards. The CPU block comprising of CPU, RAM, control-FPGA and ROM (containing boot program) are on one of the mezzanine boards. The CPU is a Freescale ACPM P1012 containing a single PowerPC (e500) core. The second mezzanine board contains power-circuitry for the module.

# 2.2.1 Main Firmware Components On Board

- 1. Boot program stored in ROM, which helps load the main application image from the system card.

- 2. VxWorks base operational Image

- 3. Application binary that runs as a loadable VxWorks Module.

- 4. FPGA image for the Sitar FPGA.

### 2.3 Module Ports & Interfaces

#### 2.3.1 Data Ports

The module has 2 pairs of client & line ports located on the front side. Being a transponder the TR10\_4EN exchanges information between client port and line ports. Signal/ framing formats between a client and its corresponding line port could be different.

A picture covering the front view of the card is shown below.

Fig. 4: Ports and Interfaces on the Front Panel

The association between client and line port is fixed in this module: (C1, L1) & (C2, L2). Traffic can only flow across ports in a given pair.

#### 2.3.2 Debug Port

The debug port is not expected to be used by the end customer. It is primarily there for ECI developers to collect debug information. It corresponds to vxWorks console port.

#### 2.3.3 Management Ethernet

TR10\_4EN is a line card in Apollo chassis that is configured & monitored through System card (sometimes called as RCP: Route Control Processor in ECI literature) in the chassis. The system card sends various image files, boot parameters as well as command and configuration parameters to each TR10\_4EN module.

The management Ethernet discussed above is not accessible to end users; it's part of the backplane signals running between the system card slot(s) and each line card slot.

# 2.3.4 Summary of FIPS140-2 Interfaces

| Interface/ Port        | Interface Type          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Client Port C1         | Data Input & Output     | Located on the front panel. It exchanges data traffic with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Chefft Fort CI         | Data input & Output     | customer equipment without encryption. Traffic is cross-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        |                         | connected between this client port and line port L1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Client Port C2         | Data Input & Output     | Located on the front panel. It exchanges data traffic with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SG                     | 2 ata impart of Carpart | customer equipment without encryption. Traffic is cross-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        |                         | connected between this client port and line port L2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Line Port L1           | Data Input & Output     | Located on the front panel. It exchanges OTN data traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        |                         | from remote peer always using AES256 encryption. Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        |                         | is cross-connected between this line port and client port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        |                         | C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Line Port L2           | Data Input & Output     | Located on the front panel. It exchanges OTN data traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        |                         | from remote peer always using AES256 encryption. Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        |                         | is cross-connected between this line port and client port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Debug                  | Developer Debug         | C2. This is a small form factor serial port located on the front                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Debug                  | Developer Debug         | panel that is used by R&D and manufacturing personnel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |                         | for low level debugging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IS LED                 | Status output           | This is a green LED on the front panel indicator showing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10 ===                 | Status Suspens          | 'in-service' status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SW-U LED               | Status output           | This amber colored LED indicates the state of F/W health                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | interface               | on the card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FAIL LED               | Status output           | This module colored LED indicates h/w health of the card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | interface               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power Input            | Power Input             | The card draws its power from the backplane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Logical Control        | Control input           | This is a logical control messaging channel that uses the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Channel                |                         | management Ethernet physical link between the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Daalmlana              | Cantual Import          | card and TR10_4EN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Backplane<br>Encrypted | Control Input           | This is an encrypted logical channel that uses the physical Ethernet link between the system card and TR10_4EN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Channel                |                         | AES256-GCM keys for encryption/ decryption of the data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chamici                |                         | traffic are input into TR10 4EN using this channel by the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        |                         | application running on the system card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        |                         | approximation of the second contract of the s |